1. 计算机系统概述 #

历史: 电子管-晶体管-(小/大规模)集成电路

高频考点:

1.1 计算机系统层次结构 #

1.1.1 计算机系统的基本组成 #

硬件 + 软件

1.1.2 计算机硬件基本组成 - 冯诺依曼结构 #

- 组成: 运算器-存储器-控制器-输入-输出

- 存储器

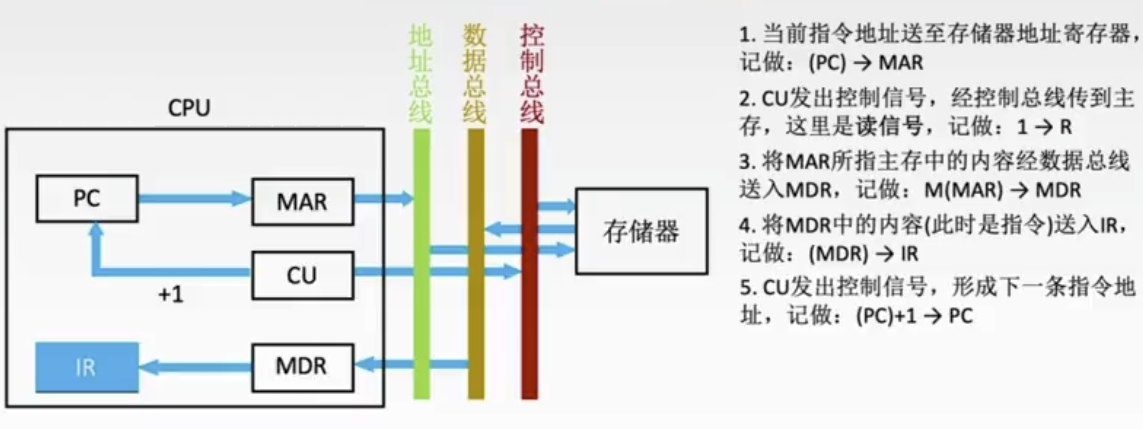

- MAR - Memory Adress Register 地址寄存器

- MDR 数据寄存器

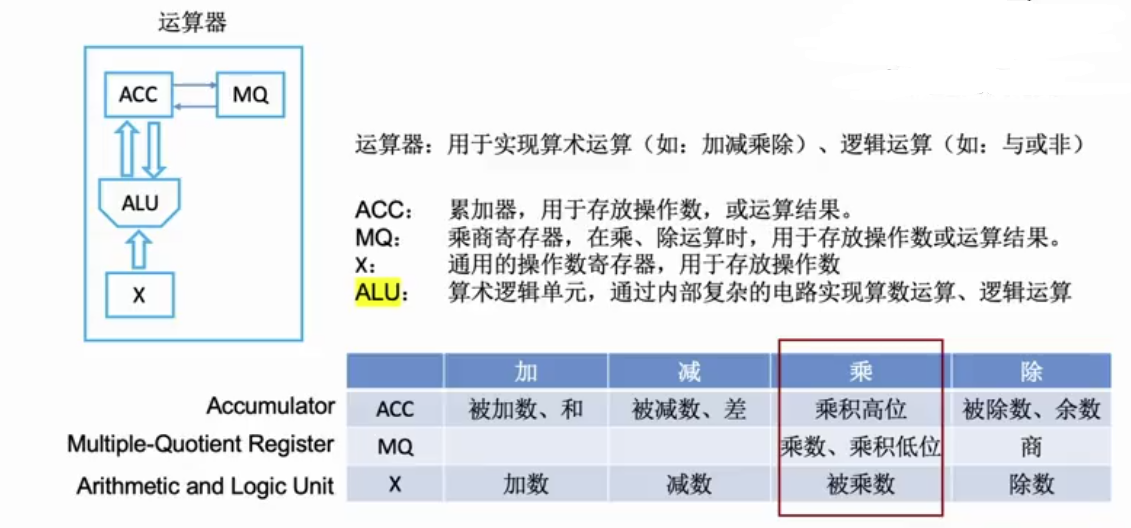

- 运算器

- ALU 算数逻辑单元

- 寄存器

- ACC 累加器

- MQ 乘商寄存器

- X 操作数寄存器

- IX 变址寄存器

- BR 基址寄存器

- PSW 程序状态寄存器 - 标志寄存器

- 控制器

- PC 程序计数器 - 存放当前要执行指令的地址(通往 MAR)

- IR 指令寄存器 - 存放当前的指令(通往 MDR)

- CU 控制单元

- 存储器

- 指令和数据以同等地位存储在存储器中, 可按地址访问

- 指令和数据均用二进制代码表示

- 指令由操作码和地址码组成; 操作码指出操作类型, 地址码给出操作数的地址

1.1.3 计算机软件和硬件的关系 #

- (系统/应用)软件

- 语言

- 机器语言 - 机器直接执行的二进制代码

- 转换为机器语言的过程成为翻译, 分为两种

- 编译 - 翻译形成新的机器语言文件再执行

- 解释 - 先执行, 执行一句, 翻译一句

- 转换为机器语言的过程成为翻译, 分为两种

- 汇编语言 - 简单英文助记符代替二进制的指令代码, 需要经过汇编转换为机器语言

- 高级语言 - 如 C 语言, 需要经过编译转为汇编语言,再经过汇编转换为机器语言

- 机器语言 - 机器直接执行的二进制代码

1.1.4 计算机系统的工作原理 #

1.2 性能指标 #

- 字长

- 机器字长 - 计算机能直接处理的二进制数据的位数

- 如 ALU、通用寄存器位数与机器字长相等

- 指令字长 - 一个指令字中包含的二进制代码的位数

- 一般取存储字长的整数倍; 以 2 倍为例, 取指周期为机器周期的 2 倍

- 存储字长 - 一个存储单元存储的二进制代码的长度

- 机器字长 - 计算机能直接处理的二进制数据的位数

- 吞吐量 - 系统单位时间内处理请求的数量

- 时钟周期

- 主频 - CPU时钟频率, 时钟周期的倒数(即一秒多少个周期)

- CPI 每条指令所需时钟周期数(与指令集, 系统结构都有关, 一般取平均)

- IPC 即 CPI 的倒数

- CPU 执行时间 = 指令数 * CPI * 时钟周期

- IPS 每秒执行多少条指令, IPS = 主频 / CPI (MIPS 每秒xx百万指令)

- (M/G/T/P)FLOPS 每秒xx(百万/十亿/万亿..)次浮点运算

2. 数据的表示和运算(重点) #

高频考点:

- 定点数编码

- 浮点数IEEE754标准表示

- 符号扩展, C语言类型转换, 数据的存储与排列

- 定点数的移位运算

- 溢出判断

- 补码加减法运算

2.1 数制与编码 #

2.1.1 进位计数制及其相互转换 #

数制之间的转换(重点)

- 整数部分除基取余

- 小数部分乘基取整

2.1.2 定点数的编码表示 #

真值: 带符号的自然数

机器数: 自然数 “01” 化后的表示, 分为两类

c 语言部分变量类型代表的长度:

- short - 16位

- int - 32 位(属于带符号数, 计算机内除浮点数外带符号数都用补码表示)

定点数(小数点的位置固定)的表示:

- 无符号数

- 有符号数 - 符号位, 0 正 1 负, 有四种编码方式(正数均等同于原码):

- 原码: 常规最高位位符号位, 但不利于加减法操作(例如减法要先比较大小再大减小)

- 反码: 原码符号位不变, 其他位取反

- 补码: 反码 + 1 (模 - a的绝对值 = a的补码)

- 使用补码可以将建房转变为等价的加法

- 此时符号位也要参与运算(数论推导), 超过八位会保留低位

- 从而 ALU 只需实现加法

- 移码: 补码的基础上将符号位取反(只能用于表示整数)

定点数的移位运算:

- 算数移位(符号位不动,正数均补0, 以下讨论负数):

- 原码: 右移, 高位补 0, 低位舍弃, 左移相反; 若舍弃位不为 0, 则丢失精度

- 反码: 右移, 高位补 1, 低位舍弃

- 补码: 右移, 高位补 0, 低位舍弃(补码转反码找最低位的0)

- 带符号数默认补码

- 真值直接转补码技巧

- 例如 -8190 补码 = $-2^{13} + 2^1$

- 即补码为

10 0000 0000 0010 - 负数符号扩展到 16 位

1110 0000 0000 0010

- 逻辑移位 - 无符号数的算数移位, 即直接从最高位开始移位

- 循环移位

- 不带进位位 - 移出的位放入移入的位

- 带进位位 - 溢出的位放到进位位, 原进位位补上空缺

例题1: 若 short 型变量 x = - 8190 , 则 x 的机器数是 E002H

2.2 运算方法和运算电路 #

2.2.1 基本运算部件 #

2.2.2 加/减运算(高频) #

原码:

- 原码的加法运算(若直接加有符号位存在会出问题),根据被加数和加数正负分:

- 正 + 正, 绝对值做加法, 符号为正, 可能会(向上)溢出

- 负 + 负, 绝对值做加法, 符号为负, 可能会(向下)溢出

- 正 + 负 | 负 + 正, 绝对值大减绝对值小, 符号为同绝对值大数

- 原码的减法操作, 转为加法(取反加一)即可

补码: 带符号位直接加

溢出问题:

- 双符号位, 通过两位异或运算判断低位是否发生溢出(溢出发生时, 可以右移一位挽救)

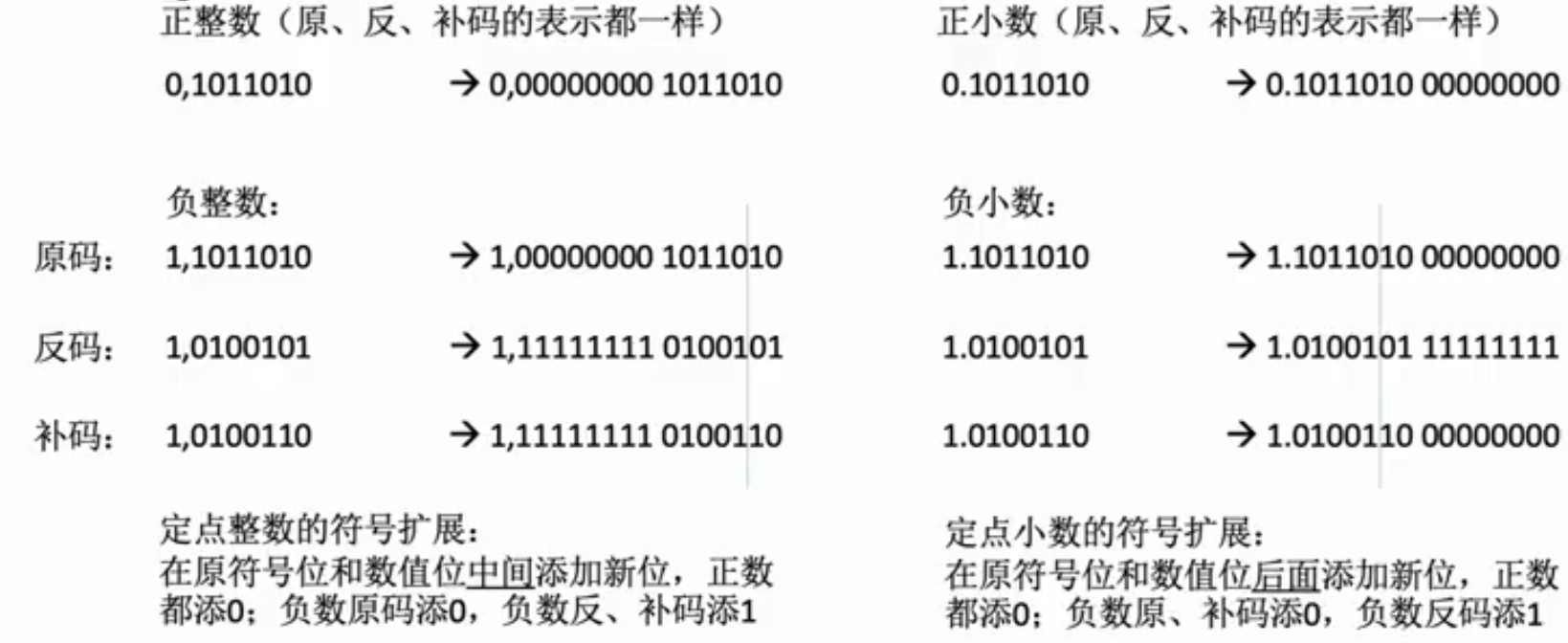

- 符号扩展(如8位扩16位)

溢出检测:

- 一位符号位

- 双符号位

- 一位符号位根据最高数位的进位

例题(Todo):

例题

加法器设计 #

$C_n$ 为最高位的进位

$C_{n-1}$ 为次高位的进位

$C_{out} = C_n$

$C_{in}$ 等同于 Sub (减法, 代表要取反加一)信号

ZF - Zero Flag, 结果为 0, ZF = 1

OF - Overflow Flag, 溢出标志 = $C_n \otimes C_{n-1}$

SF - Sign Flag, 结果最高位(双符号位时取最高位)

CF - Carry Flag, 借位标志 = $Sub \otimes C_{out}$

2.2.3 乘/除运算 #

乘法参考

除法参考辗转相除法

原码的一位乘法:

- 符号位单独异或运算, 数值取绝对值乘法计算

- n次"加法(二进制下, 最高位1加被乘数, 最低位0则加0)+逻辑右移(高位补0)"

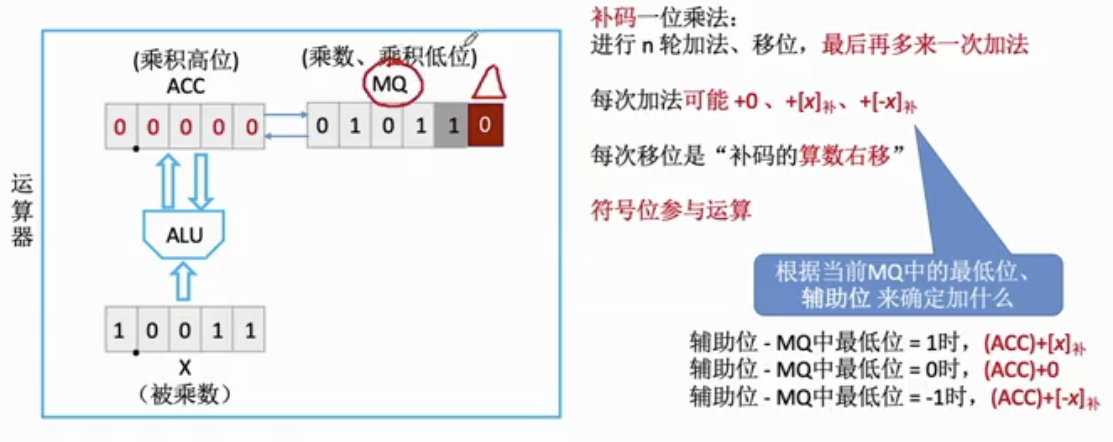

补码的一位乘法(Booth算法):

- 符号位参与运算,新增一个标志位, 乘数右移y后移入

- 进行 n 论加法算数右移, 最后按照规则再多来一次加法

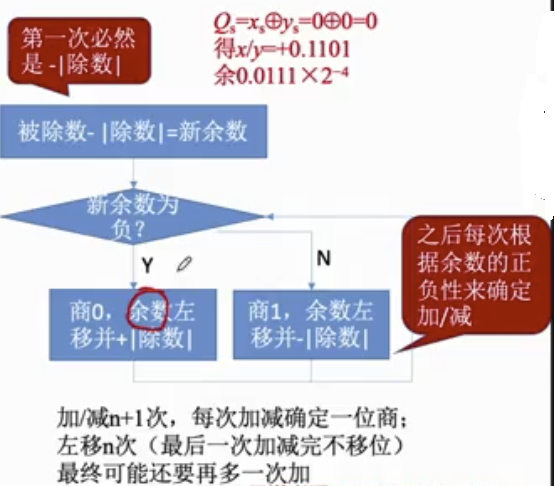

原码除法(TODO):

- 恢复余数法

- 符号位单独异或运算, 数值取绝对值除法计算

- n 次 “减法+逻辑左移(低位补0)”, mo

- 加减交替法(恢复余数法的优化)

- 符号位单独异或运算, 数值取绝对值除法计算

-

补码除法: 加减交替法(TODO)

- 符号位参与运算, 被除数/余数, 除数采用双符号位

2.3 整数的表示和运算 #

按考纲组织的无符号/带符号整数的表示和运算上述已经介绍过

2.3.1 无符号整数的表示和运算 #

2.3.2 带符号整数的表示和运算 #

2.4 浮点数的表示和运算 #

2.4.1 浮点数的表示 #

$浮点数 = r^{阶码} \times 尾数$, 其中 r 位进制数:

- 阶码(阶符(号) + 阶码数值), 常用补码或移码, 反映大小

- 尾数(数符(号) + 尾数数值), 常用补码或原码, 反映精度

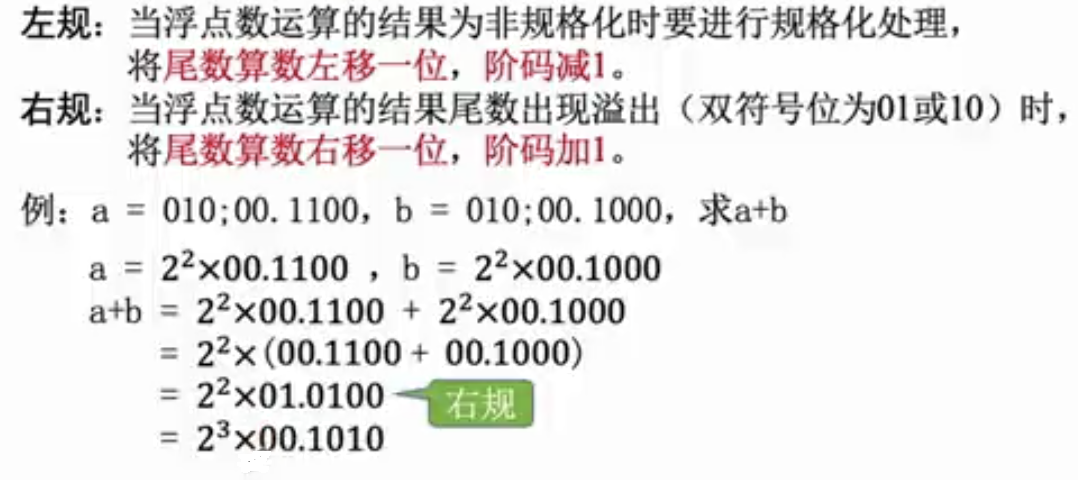

由于精度不一, 遂规格化(类似科学计数法最高位不能为 0):

- 左规 - 尾数左移一位, 阶码减 1

- 右规 - 尾数右移一位, 阶码加 1

规格化后特点:

- 原码

- 正数 - 0.1xxx

- 负数 - 1.1xxx

- 补码(补码负数: 算数左移, 低位补 0; 算数右移, 高位补 1)

- 正数(同原码) - 0.1xxx

- 负数 - 1.0xxx, 最大值 1.01..1, 最小值 1.00..0

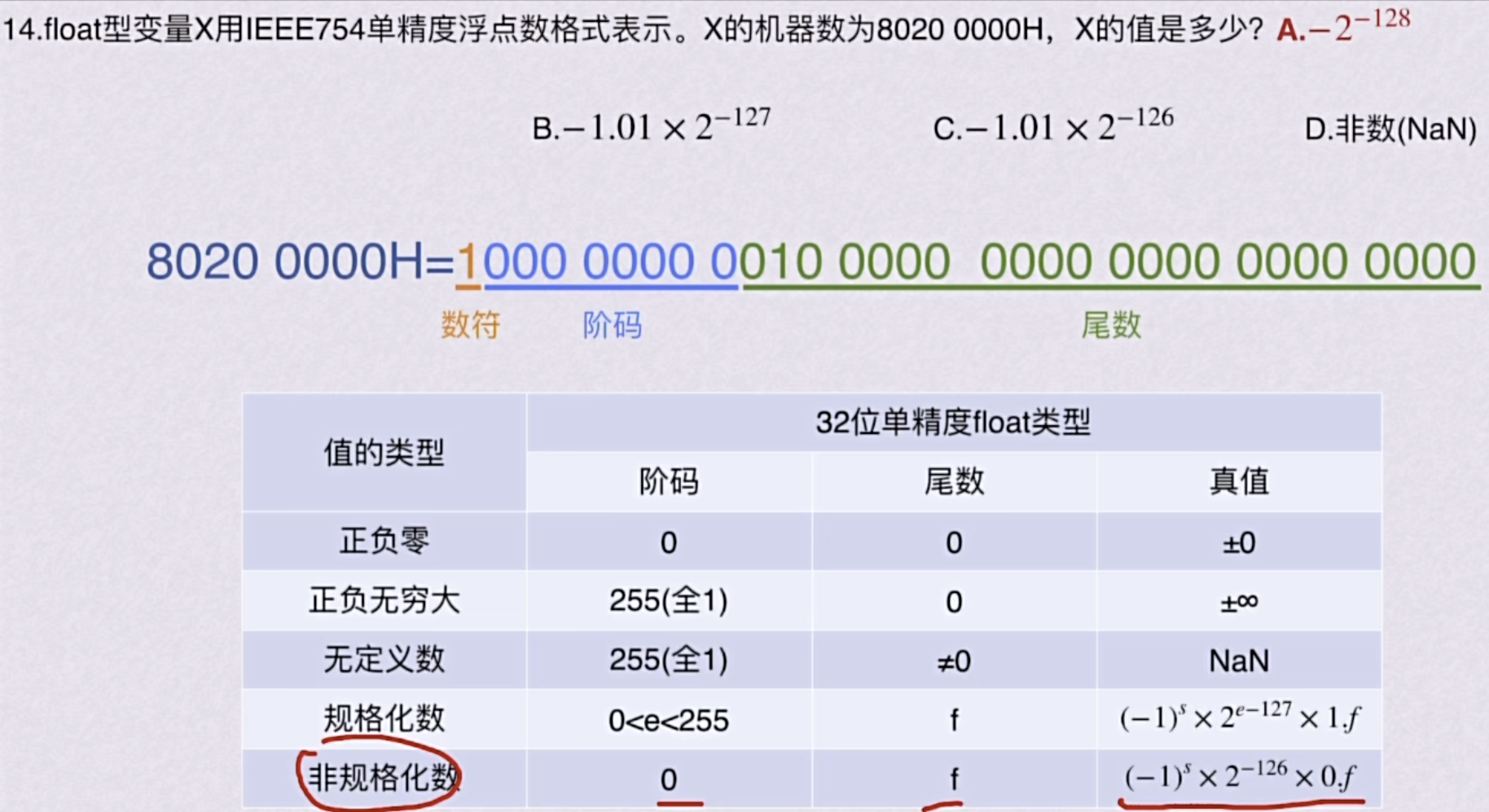

IEEE-754 #

IEEE-754 单精度浮点数格式标准:

- 1 位数符(正负)

- 8 位阶码(移码-补码基础上符号位取反)

- 23 位尾数(补码)

非规格例题:

2.4.2 浮点数的加/减运算 #

- 对阶 - 对齐为 2 的 n 次方, 小阶向大阶靠齐

- 尾数相减

- 规格化

- 舍入(若规定保留x位有效尾数, 可以直接砍掉或四舍五入)

- 判溢出(阶码进位溢出; 尾数溢出可以通过规格化补救)

真题例题 #

(2001真题)设浮点数的阶码和尾数均采用补码表示,且位数分别为5位和7位(均含2位符号位). 若有两个数$X = 2 ^ 7 \times \frac{29}{32} , Y = 2 ^ 5 \times \frac{5}{8}$ 则用浮点加法计算X+Y的最终结果是?

解(以下用``;`分隔和尾数):

- 规格化

- X的阶码为 7, Y 的阶码为 5, 小阶向大阶靠齐

- 即 Y 的阶码加 2, 尾数右移 2 位

- Y 的尾数: $\frac{5}{8} = \frac{1}{2^1} + \frac{1}{2^3}$, 用7位补码(正数同原码)其中2位符号位表示:

- 00.10100

- 右移两位为: 00.00101

- X 的尾数: 00.11101

- 尾数相加

00.10100+00.11101=01.00010- 溢出了一位到符号位, 所以需要右规

- 规格化

- 尾数相加溢出一位, 右规阶码加 1

- 原 X 阶码5位补码表示:

00111 - 加 1 后

01000

- 原 X 阶码5位补码表示:

- 尾数右移一位:

00.10001 - 即结果:

01000;00.11001

- 尾数相加溢出一位, 右规阶码加 1

- 判溢出, 阶码符号位为

01, 因此结果溢出了(如果左归则尾数溢出)

3. 存储系统(重点) #

3.1 存储器的分类 #

按存储介质分类:

- 半导体(内存)

- 磁性材料(机械硬盘)

- 光介质(光盘)

按存储方式分类:

- RAM - 随机存取存储器(读写时间位置无关, 如内存)

- SAM - 顺序存取存储器(读写时间与位置相关, 如磁带)

- DAM - 直接存取存储器(位置部分相关, 如磁盘)

按信息的可更改性:

- 读写存储器

- 只读存储器 - ROM(如 BIOS CD_ROM)

按照信息的可保存性:

- 易失性存储器(断电丢失)

- 非易失性存储器(断电保存)

存储器的性能指标:

- 存储容量 = 存储字数 x 位数

- $存取周期T_m = 存取时间T_a + 恢复时间$

- 存储速度(数据传输率/带宽) = 数据的宽度 / 存储周期

3.2 存储器的层次化结构 #

存储器按靠近 CPU 的顺序依次为(速度依次变慢):

- 寄存器

- Cache

- 主存(内存)

- 辅存(硬盘)

- 外存(u盘等)

3.3 半导体随机存取存储器 #

3.3.1 SRAM 存储器 #

非破坏性读出, 无需回写, 速度块; 体积大(6 MOS)

常用作 Cache

只要一直通电就不需要刷新

送行列地址: 同时送(容量一般不大)

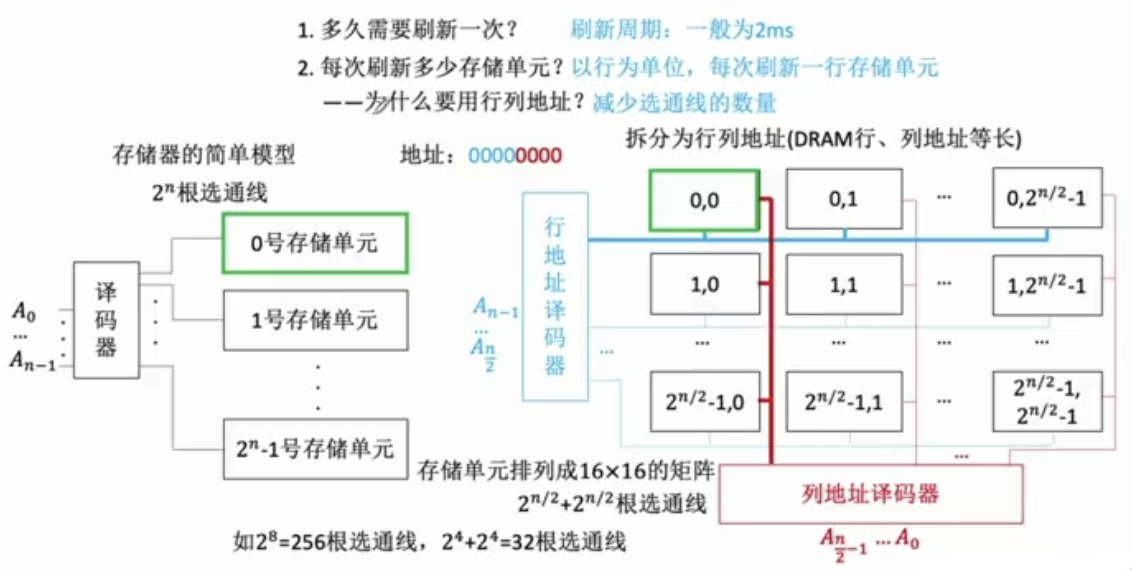

3.3.2 DRAM 存储器 #

破坏性读出(电容放电), 读出后需要回写, 速度变慢; 体积小(1个 MOS)

常用作主存(内存)

电容内的电荷通常只能维持 2ms, 在此期间必须刷新:

刷新 = 1次读 + 1次写, 占用一个读/写周期

刷新时机策略:

- 分散刷新 - 每次读写完都刷新一行

- 集中刷新 - 2ms内集中安排时间全部刷新(期间无法访问存储器)

- 异步刷新 - 2ms 内(利用CPU不需要访问存储器的时机)每行刷新一次即可

送行列地址: 共用一条地址线, 两次传输, 地址线减半, 引脚减少

3.3.3 Rom(大纲为 Flash 存储器) #

各类 ROM:

- MROM - 掩模式ROM, 生产过程写入, 之后不可重写

- PROM - 可编程ROM, 可写一次, 之后只读

- EPROM - 可擦除可编程 ROM

- UV EPROM - 紫外线擦除, 只能全部擦除

- E EPROM - 电擦除, 可部分擦除

Flash 即基于 EEPROM 发展而来

由于闪存需要先擦除再写入, 因此 “写” 速度比 “读” 速度更慢

计算机内 Rom 即存储 BIOS, 内存 + ROM 为主存

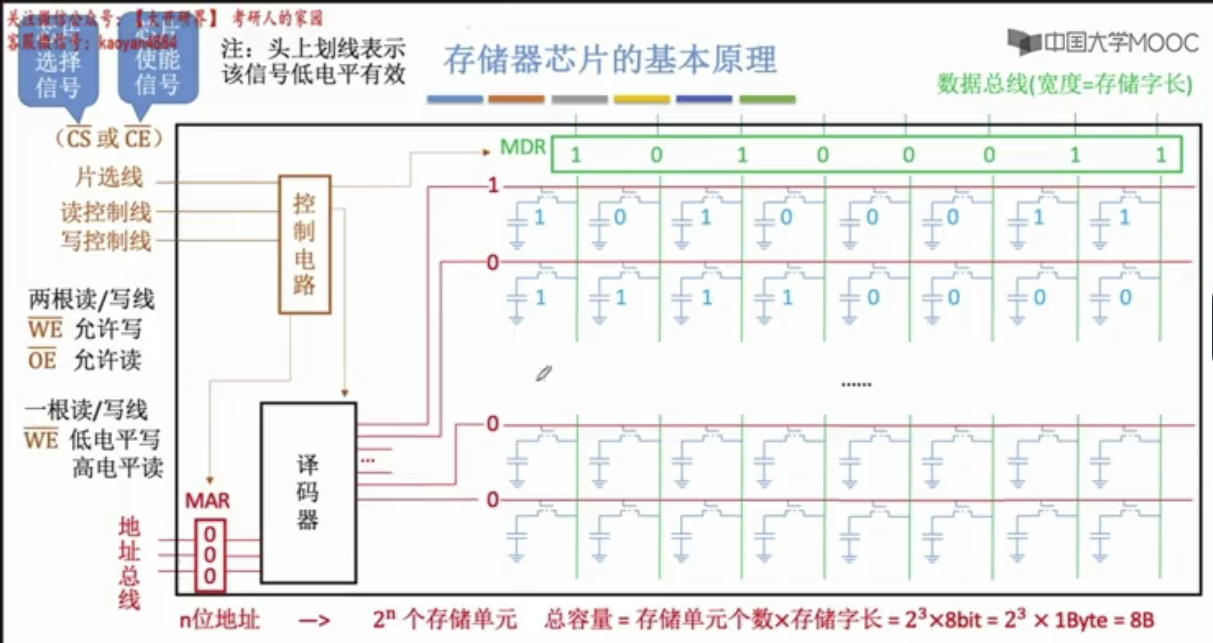

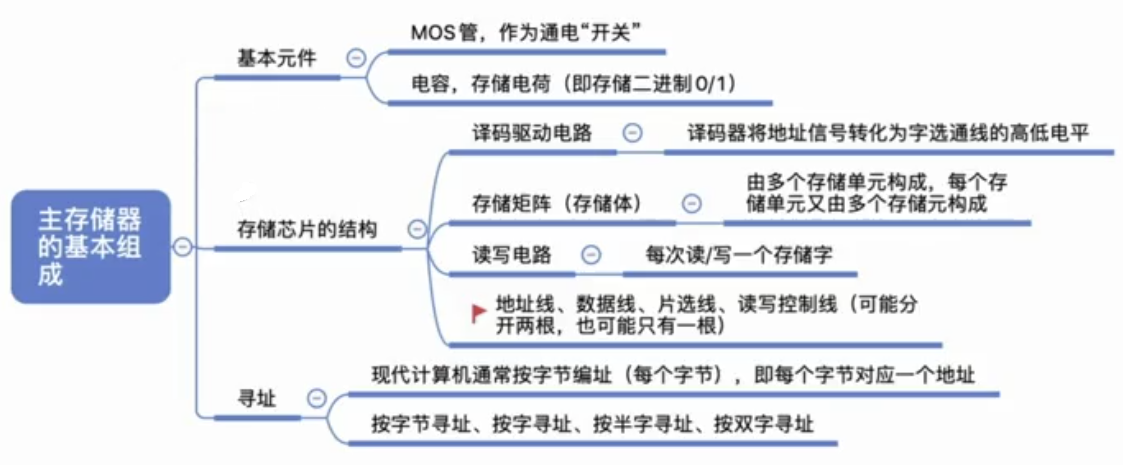

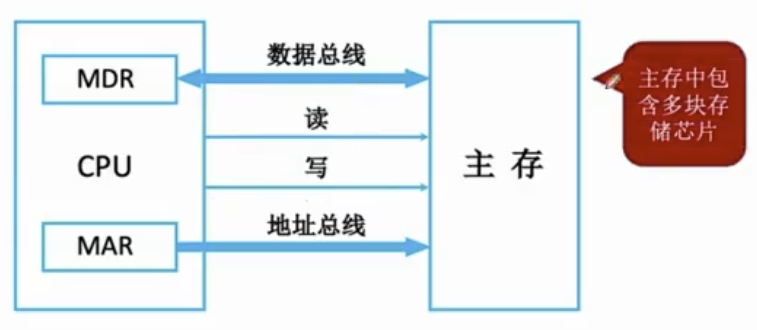

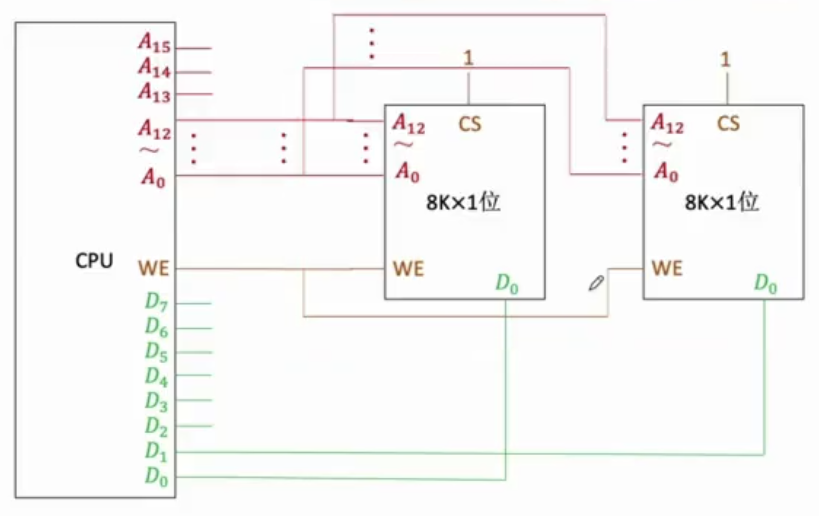

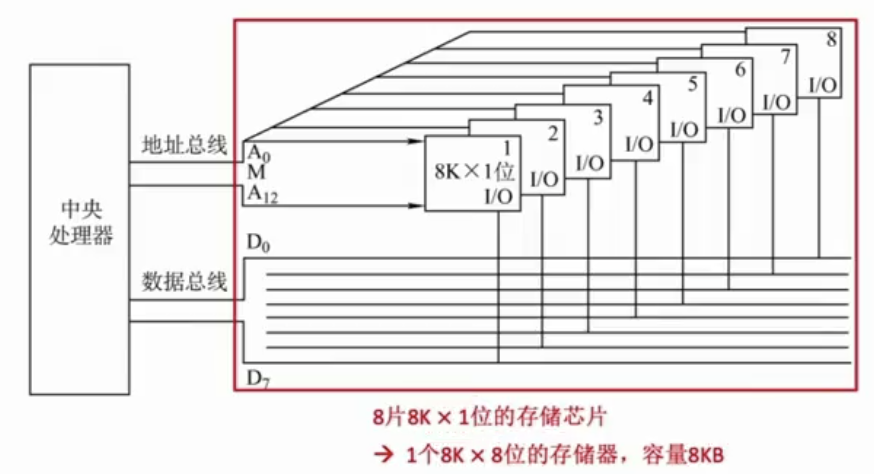

3.4 主存储器(重点) #

数据线的根数 = 存储芯片的位数

n 个地址线(0|1两种状态)可以表示 2^n 个地址数(状态)

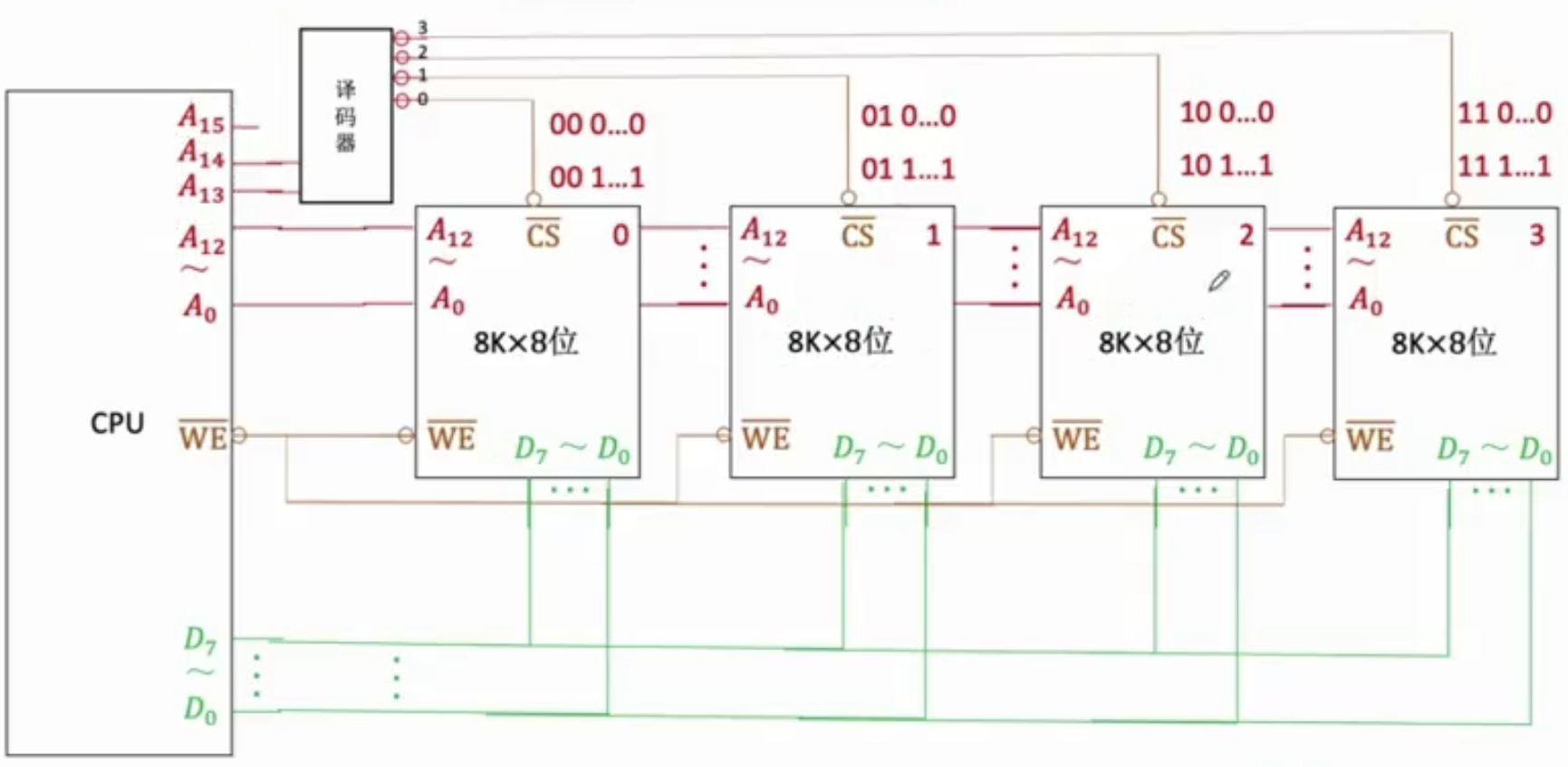

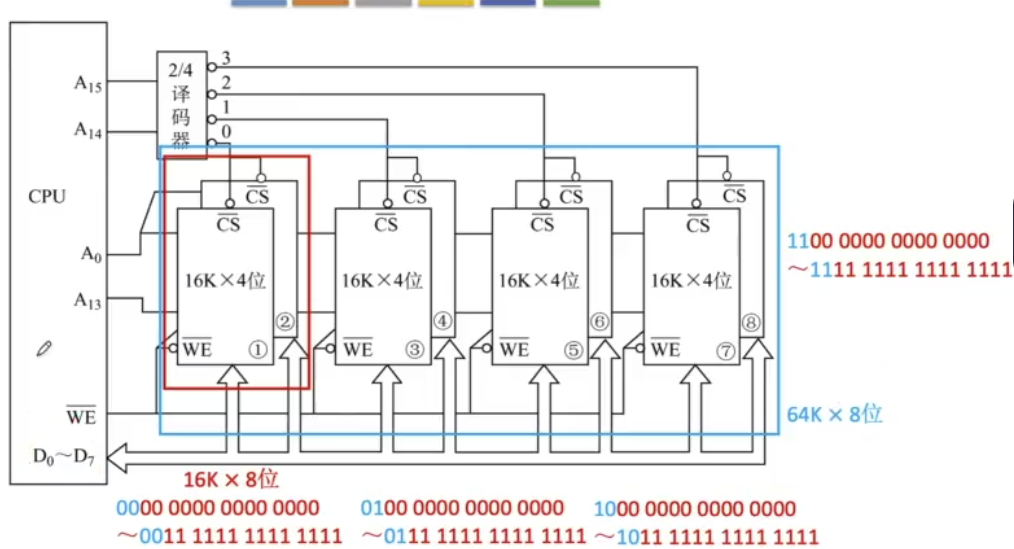

总结:

例题: 地址范围 0H-FFFFH, 16 位字长的存储器, 需要多少片 8k x 8 位的 RAM 芯片组成

- 所需芯片数 = 目标存储容量 / 芯片单位容量

- 存储容量 = 字数 x 位数

- 存储器容量: 64k x 16

- 字数 = (FFFFH - 0H) = 64k 字

- 位数 16

- 单个芯片容量: 8k x 8

- 存储器容量: 64k x 16

3.4.1 DRAM 芯片和内存条 #

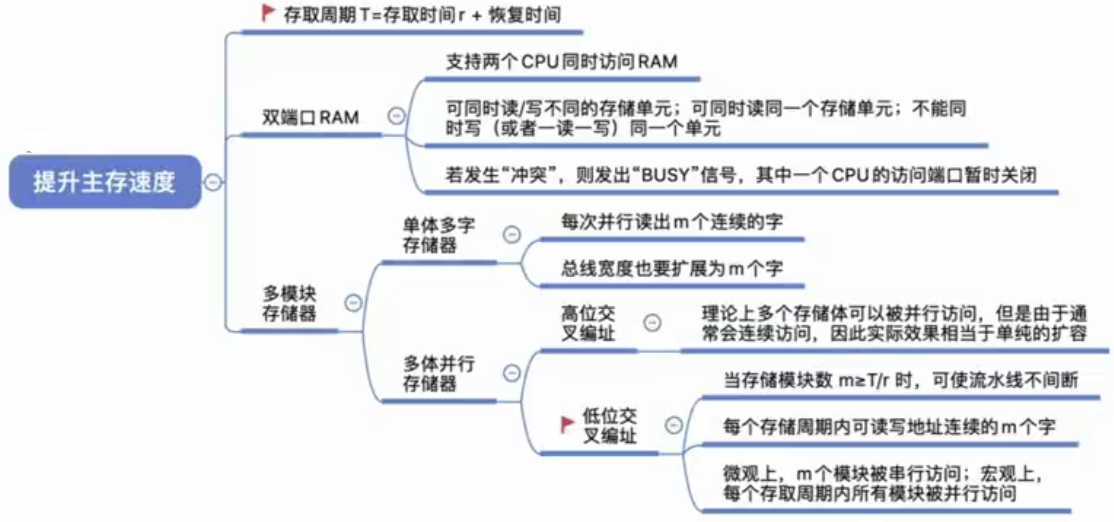

3.4.2 多模块存储器 #

3.4.3 主存和 CPU 之间的连接 #

例题 #

主存容量的扩展 #

位扩展 #

字扩展 #

译码片选法(即用译码器, 还有线选法, 缺点是地址浪费不连续)

字位扩展(重点) #

主存速度的提升 #

双端口 RAM() #

优化多核 CPU 访问同一根内存条的数据

重点在于同时访问时的读写冲突

多体并行存储器 #

多根内存条

高位交叉编址:

- 利用高位表明存储在第几个存储单元(体号)

- 地址连续, 顺序存取

- 不能并行访问, 不能提升吞吐率

低位交叉编址: - 低位地址表明存储在第几个存储单元

- 地址离散, 随机存取

- (连续访问时)双通道并行访问, 提升吞吐率

消费级计算机主板上, 01和23为一组, 组内高位交叉编址, 组间低位交叉编址

3.5 外部存储器 #

3.5.1 磁盘 #

3.5.2 SSD 固态硬盘 #

控制单元 + 多个闪存芯片

3.6 高速缓冲存储器-Cache(重点) #

3.6.1 Cache 基本原理 #

局部性原理 #

- 空间局部性 - 即将要用到的数据可能就在现在读取数据的周围

- 如何界定周围的数据 - 分块/行/页(例如以 1KB 为单位读取)

- 时间局部性 - 现在用的数据可能等下还会用

因此现在用的数据临时存储在高速存储中可以加速整体运行速度

两种读策略 #

- 先访问 cache, 未命中再访问主存(再复制到 cache)

- 同时访问, 若 cache 未命中再停止访问主存

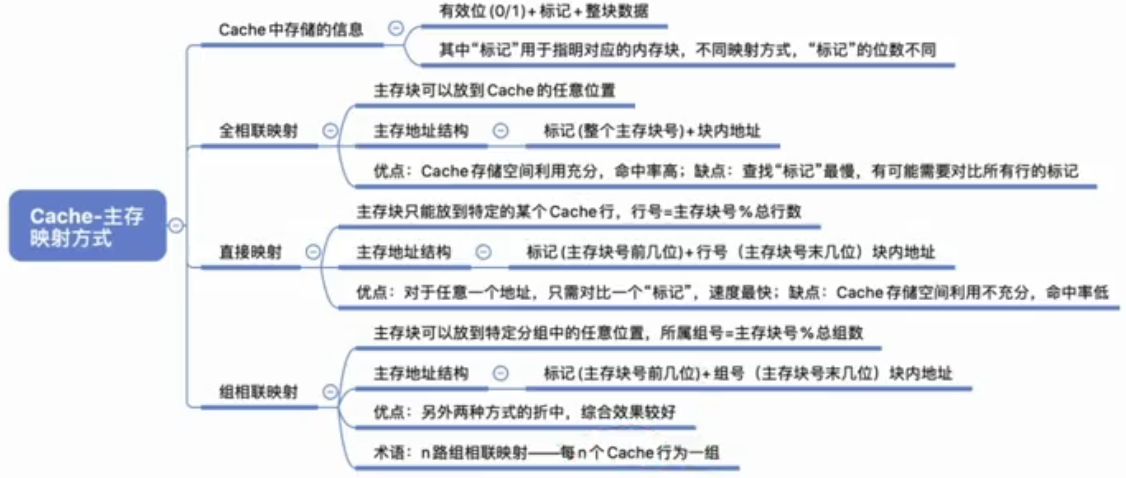

3.6.2 Cache 和主存之间的映射方式(重点) #

标记位: 标记 cache 块对应主存中的地址

全相联映射 #

主存块可以放置到 Cache 的任意位置

Cache 块和主存块大小相等

地址结构: 标记 + 块内地址

直接映射 #

每个主存块只能放到特定的位置 = 主存块号 % cache 总块数n

缺点: cache 空间利用率低

优点: cache 标记位变小

地址结构: 标记 + 块号(行号) + 块内地址

例题 #

假定主存地址为32位,按字节编址,主存和 Cache 之间采用直接映射方式, 主存块大小为4个字,每字32位,采用回写(Write Back) 方式,则能存放 4K字数据的 Cache的总容量的位数至少是多少?

- 确定块内地址位数(由块大小决定)

- 块大小 = 字数 x 位数 = 4 x 32位(即 4B) = 16B

- 需要 4 位表示 16 字节的地址偏移量(按字节编址)

- 确定块号(行号)位数

- 即 4K 字数据(16KB)需要多少块存储, 因此需要 1K 块(行)

- 故需要 10 位(2^10) 表示 1K 行

- 标记位 = 32 - 4 - 10 = 18 位

- cache 中每一行的位数 = 16B(数据部分) + 18位(标记位) + 1(状态位) + 1(脏位) = 148 位

- 总容量即 1k 行的位数 = 148 k

若计算机主存地址为32位,按字节编址,Cache 数据区大小为32KB, 主存块大小为32B, 采用直接映射方式和回写(Write Back)策略,则Cache行的位数至少是多少?

- 确定块内地址位数(由块大小决定)

- 块大小 =

组相联映射 #

Cache块分组, 组号 = 主存块号 % cache 总组数 n

主存块可放到对应分组的任意位置

地址结构: 标记 + 组号 + 块内地址

3.6.3 Cache 中贮存块的替换算法 #

Cache满了如何处理 - 替换算法

注意直接映射只能替换固定位置, 不需要算法

随机 #

实现简单, 没有考虑局部性原理, 命中率低

先进先出(FIFO) #

实现简单, 没有考虑局部性原理, 命中率低

最近最少用(LRU) #

计数器记录该行最近访问后的时间, 替换计数器最大的一行

效果优秀, 命中率高

最不经常使用(LFU) #

记录器记录该行被访问过的次数, 替换计数器最小的一行

没有较好的考虑局部性原理, 效果不如 LFU

3.6.4 Cache 写策略 #

CPU修改了Cache中的数据副本, 确保主存中数据一致性

根据写操作是否命中 cache, 分两种情况

写命中 #

- 写回法(Write back) - 只修改 cache, 此块被换出时才写回主存

- 全写法 - 同时写入 cache 和主存

- 为了减少全写的时间消耗, cache和主存直接会增加一个写缓冲

写不命中 #

- 写分配法 - 主存的块调入 cache, 在 cache 中修改, 常搭配写回法

- 非写分配法 - 只写入主存, 常搭配全写法

3.7 虚拟存储器(操作系统第三章重合) #

3.7.1 虚拟存储器的基本概念 #

虚拟存储器将主存(内存)和辅存(硬盘)地址空间统一编址, 将实际物理存放地址抽象为虚地址

3.7.2 页式虚拟存储器 #

一个进程逻辑上被分为若干大小相等的 “页”, 大小同块大小, 每个页可以离散的放入不同的主存块中, 主存的页成为实页, 辅存的页称为虚页

缺点: 页的大小固定, 容易不匹配实际情况而浪费

页表 #

存放于主存中, 记录虚页被调入主存时的位置

行组成:

- 有效位 - 表示页面是否装在主存

- 脏位 - 是否修改过(配合写回法写回磁盘)

- 引用位 - 配合 FIFO 或 LRU 等替换策略存储对应信息

- 内容 - 已调入主存则存放物理页号; 否则存放地盘地址

每个进程都有一个页表基址寄存器, 表明页表在主存中的存放地址(起点), 这样页表内只需要存储相对起点的偏移量即可

基本原理, 页表, 地址转换, TLB快表

TLB 快表 #

Todo

3.7.3 段式虚拟存储器的基本原理 #

段长按照程序逻辑结构划分

虚拟地址由段号和段内地址组成

缺点: 碎片化

段表 #

实现虚拟地址到实地址之间的转换

相比页表, 其存储项多了段长

3.7.4 段页式虚拟存储器的基本原理 #

先按逻辑结构分段, 每段再划分固定大小的页(主存块大小与之对应)

每个程序(进程)对应一个段表, 每段对应一个页表

虚地址: 段号 + 段内页号 + 页内地址

访问虚地址时:

-

根据段号拿到段表地址

-

从段表取出该段页表的起始地址

-

与段内页号合成, 得到页表地址

-

从页表中取出实页号

-

与业内地址合成, 得到主存实地址

-

存储器概述

- 存储器的分类

- 多层级的存储器

- 存储器的性能指标

-

主存储器

- 存储芯片的原理 + 元件

- RAM

- SRAM

- DRAM(刷新, 地址复用技术)

- ROM

- 多体并行存储器

- 高位交叉编址

- 低位交叉编址

-

主存储器与CPU的连接

- 位扩展

- 字扩展

- 字位扩展

-

外部存储器

- 磁盘存储器

- 固态硬盘 SSD

-

高速缓存存储器Cache(可能出大题)

-

Cache的基本概念 + 局部性原理

-

Cache 的映射方式

- 直接映射

- 全相映映射

- 组相联映射

-

Cache 的替换算法

- 随机

- 先进先出(FIFO)

- 最近最少用(LRU)

- 最不经常使用

-

Cache 的写策略

- 写命中(全写法, 回写法)

- 写不命中(写分配法, 非写分配法)

-

虚拟存储器

-

页式虚拟存储器

- 快慢表

- 具有 TLB 和 Cache 的多级存储系统

-

段式存储器

-

段页式存储器

4. 指令系统 #

4.1 指令格式的基本概念 #

通常由: 操作码 OP, 地址码 A 组成

根据指令地址码数目不同将指令分类:

- 零地址指令 -

- 无需操作数, 如停机

- 需操作数, 操作数隐含在堆栈中

- 一地址指令

- 单操作数, 如取反 - $OP(A_1) => A_1$

- 双操作数, 另一隐藏在寄存器(如ACC)中 - $(ACC)OP(A_1) => ACC$

- 二地址指令 - $(A_1)OP(A_2) => A_1$

- 三地址指令 - $(A_1)OP(A_2) => A_3$

- 四地址指令

- $(A_1)OP(A_2) => A_3$

- $A_4 = 下一条指令的地址$(非顺序执行场景)

指令长度固定时, 地址码数量越多, 则单个地址越小, 寻址能力越弱

按照操作码长度将指令分类:

- 定长操作码

- 可变长操作码

按操作类型分类:

- 数据传输(LOAD / STORE)

- 运算类

- 算术

- 逻辑

- 移位

- 转移操作 - 改变执行顺序

- 无条件转移 JMP

- 条件转移 JZ

- 调用 CALL

- 返回 RETURN

- IO(输入输出)操作

4.2 指令格式 #

4.2.1 定长操作码 #

优点: 简单, 识别快

缺点: 表达指令有限; 操作数地址位数有限

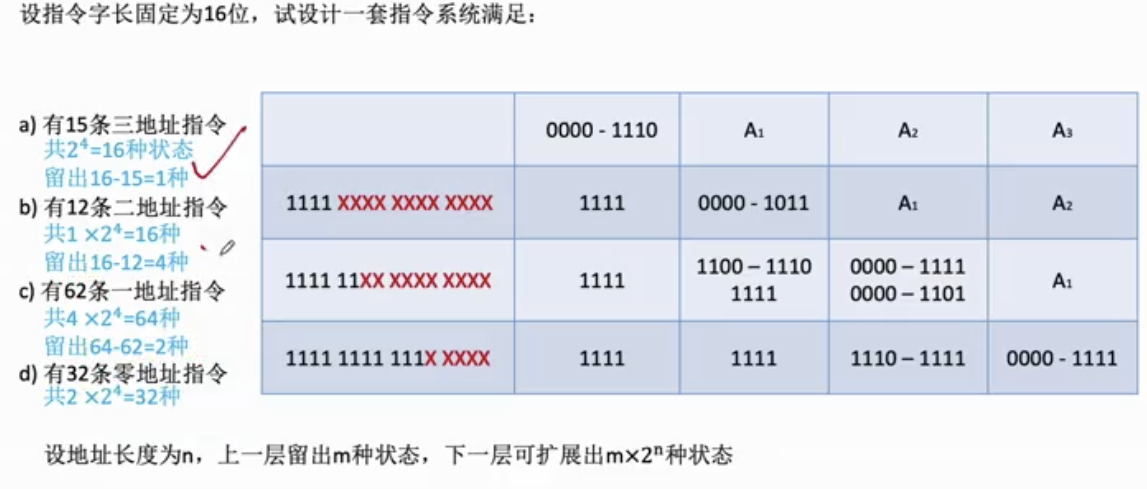

4.2.2 扩展操作码(重点) #

操作码的长度随地址码的减少而增加

短操作码不能与长操作码前面部分代码相同(例如将111留作扩展位)

应对使用频率较高的指令分配较短的操作码, 反之较长

例题:

4.3 寻址方式 #

4.3.1 指令寻址 #

CPU中用程序计数器(PC)指明下一条命令的地址

顺序寻址 #

PC 自增 1(1个指令的字长)

对于定长指令字结构:

若主存块大小 = 指令字长 = 存储字长, 每条指令读 1 次, PC 加 1

若主存按字节编址, 指令字长 = 存储字长 = 2Byte, 则每条指令需读两次, PC 加 2

对于变长指令字结构:

跳跃寻址 #

转移类指令直接修改 PC 值

4.3.2 数据寻址(重点) #

确定地址码指明的真实地址(例如相对地址)

因此指令格式中增加寻址特征(4位)表明寻址方式

以二地址指令为例, 现在的格式为:

操作码 OP + 寻址特征 + 形式地址A1 + 寻址特征 + 形式地址A2

隐含寻址 #

如单地址指令中使用 ACC 作为

立即寻址 #

存放操作数本身(一般为补码形式), 无需访问主存

直接寻址 #

形式地址即为真实地址, 类似指针

缺点: 地址码的位数决定了寻址范围; 地址不易修改

间接寻址 #

一次间接寻址: 指向操作数存储地址的地址(如主存地址的地址)

n次间接寻址即嵌套上述流程, 在主存中多次寻址(根据标记为判断是指针还是数据)

寄存器寻址 #

直接给出操作数所在的寄存器编号, 无需访问主存

寄存器少, 对应的地址码长度小

寄存器间接寻址 #

寄存器中存储的操作数在主存中的实际地址

相对寻址 #

形式地址为偏移量(补码), 以 PC 为起点

取出当前指令后, PC 会指向下一条指令

因此偏移量也是相对下一条指令的

基址寻址 #

形式地址为偏移量, 以程序的起始存放地址(基址寄存器BR)为起点

由于基址寄存器是面向操作系统的, 也可指定寄存器作为基址寄存器

此时寻址特征还需要指明寄存器地址, 长度取决于寄存器总数

利于多道程序场景

变址寻址 #

形式地址为基地址, 程序(用户)决定偏移量, 存放于变址寄存器 IX 中

同样的, 也可能操作系统没有 IX 而存放在通用寄存器中

变址寄存器是面向程序(程序员), 可以被程序运行时修改

适合循环程序, 数组问题等

多道程序+访问数组场景可思考基址&变址复合寻址

堆栈寻址 #

操作数隐含在堆栈指针(寄存器) SP 中

堆栈分两种:

- 硬堆栈 - 寄存器堆栈, 速度快, 容量低

- 软堆栈 - 主存堆栈

4.4 数据的对齐和大/小端存放方式 #

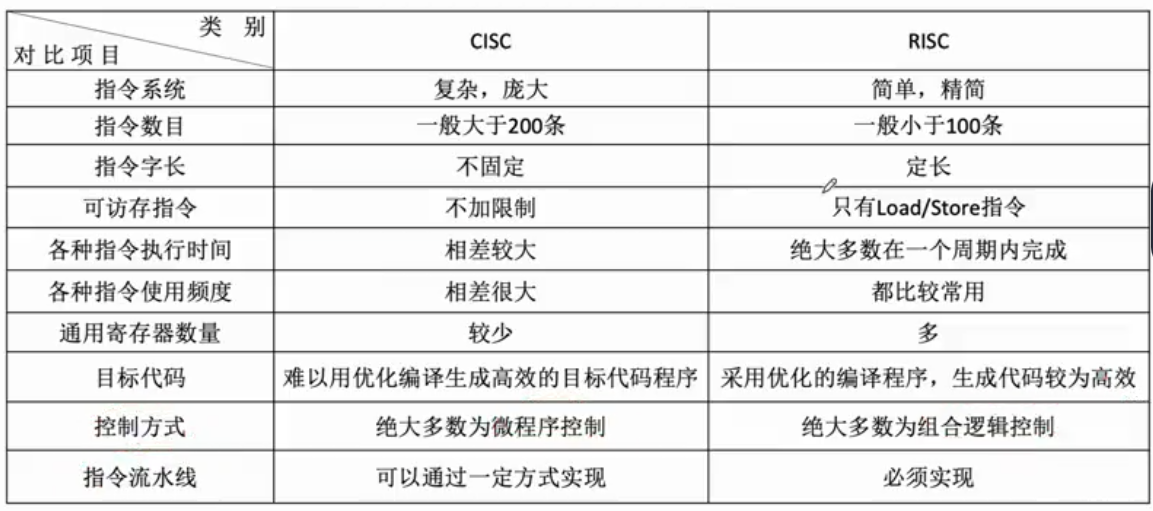

4.5 CISC和RISC的基本概念 #

CISC: 复杂指令集计算机

RISC: 精简指令集计算机

4.6 高级语言和机器码之间的对应 #

4.6.1 编译器、汇编器和链接器 #

4.6.2 选择结构语句的机器码 #

4.6.3 循环结构语句的机器码 #

4.6.4 函数调用的机器码 #

5. 中央处理器(重点) #

5.1 CPU 的功能与基本结构(控制器, 运算器) #

功能:

- 指令控制

- 取指令 - 形成指令地址, 自动发出取指命令

- 分析指令 - 操作码译码, 操作数寻址

- 执行指令

- 操作控制

- 时间控制

- 数据加工

- 中断处理

5.1.1 运算器 #

基本结构:

- 算术逻辑单元 ALU

- 暂存寄存器 Y

- 累加寄存器 ACC

- 通用寄存器组(供用户自由编程)

- 程序状态寄存器

- 移位器

- 计数器 - 控制乘除运算的操作步数

5.1.2 控制器 #

基本结构:

- 程序计数器 PC

- 指令寄存器 IR - 保存当前正在执行的命令

- 指令译码器

- 存储器地址寄存器 MAR - 要访问的主存单元的地址

- 存储器数据寄存器 MDR - 要向主存写入或从主存读出的信息

- 微操作信号发生器

- 时许系统

5.2 指令的执行过程(重点-大题) #

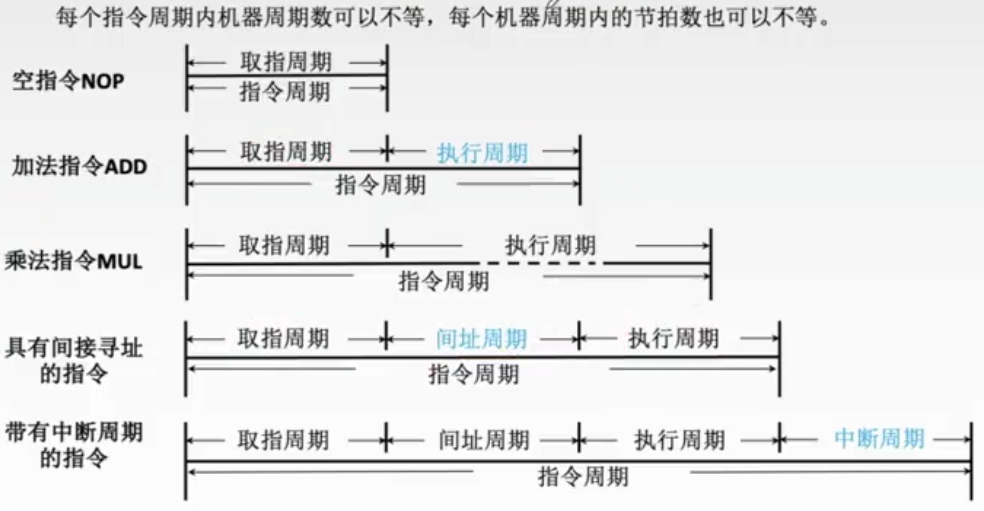

指令周期: CPU 从主存中每取出并执行一条指令所需的全部时间

机器周期 一个指令周期通常用若干个机器周期表示, 也叫 CPU 周期

时钟周期 一个机器周期包含若干时钟周期, 也叫节拍或 T 周期, 也是 CPU 操作的基本单位

不同指令的指令周期组成(4种工作周期):

考察体型: 给指令描述各个阶段的微操作(数据流和控制信号)

5.2.1 指令周期的数据流 #

为了区分不同的工作周期, CPU 内设置了 4 个标志触发器

取指周期 - FE #

从主存取出指令代码并存放在 IR 中(最后PC+1)

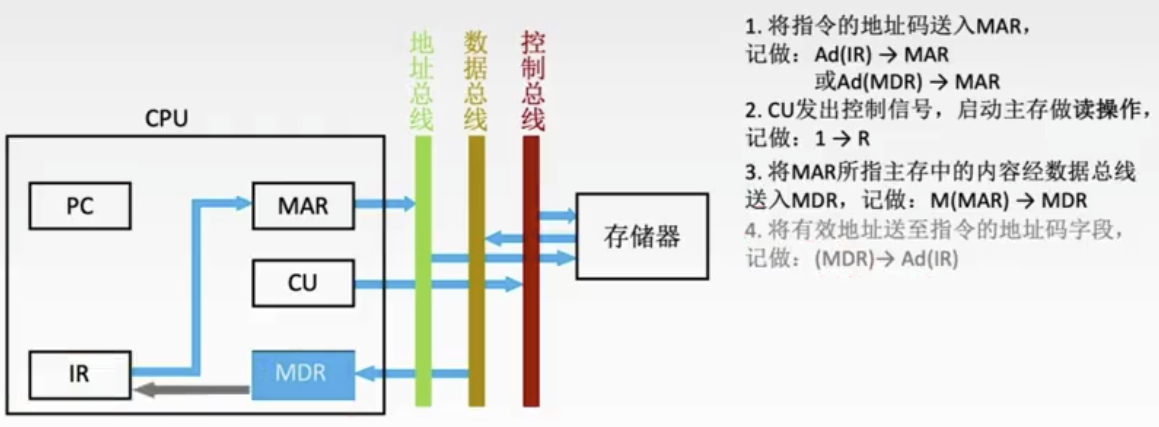

间址周期 - IND #

取操作数的有效地址, 以一次间址为例:

执行周期 - EX #

取操作数

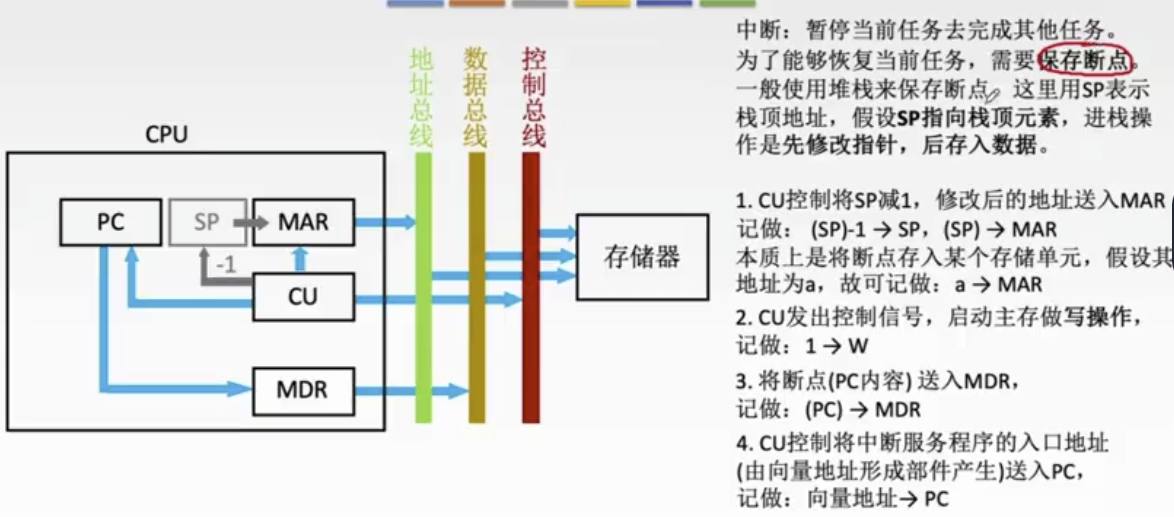

中断周期 - INT #

处理中断请求, 保留当前执行位置(上下文)

5.2.2 指令周期方案 #

单指令周期 #

所有指令选用相同的执行时间完成, 指令周期取决于耗时最长的指令

指令之间串行执行

多指令周期 #

不同指令选用不同的执行时间

指令之间串行

流水线方案 #

指令之间并行

5.3 数据通路的功能和基本结构 #

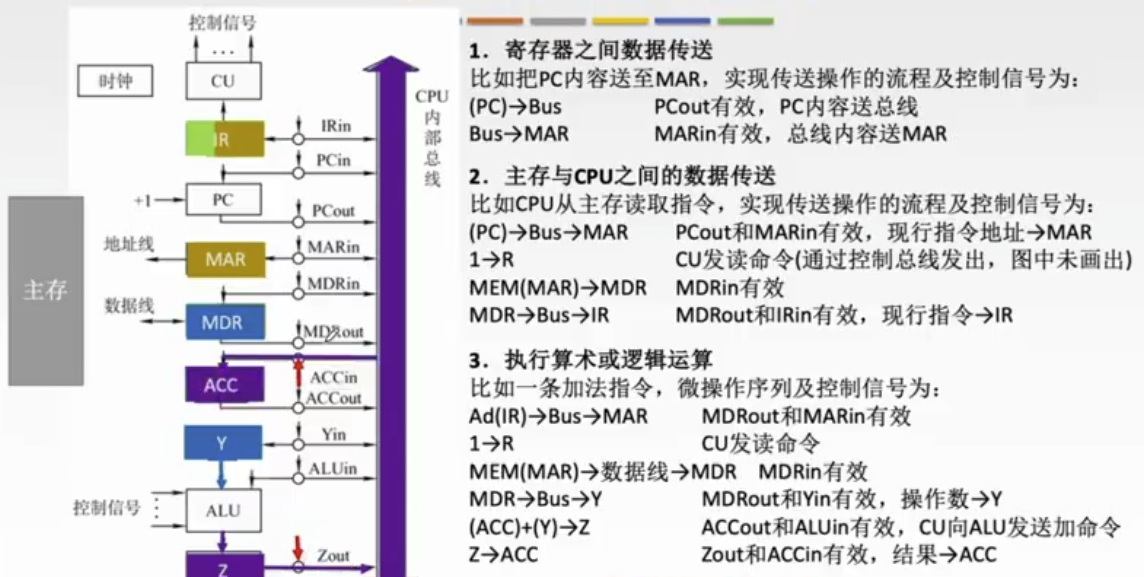

3种数据流动: 寄存器 <=> 寄存器 | ALU | 主存

数据通路: 描述信息从哪里开始, 经过哪些部件, 最后到哪里

数据通路的三种基本结构(注意CPU内部总线有别于系统总线):

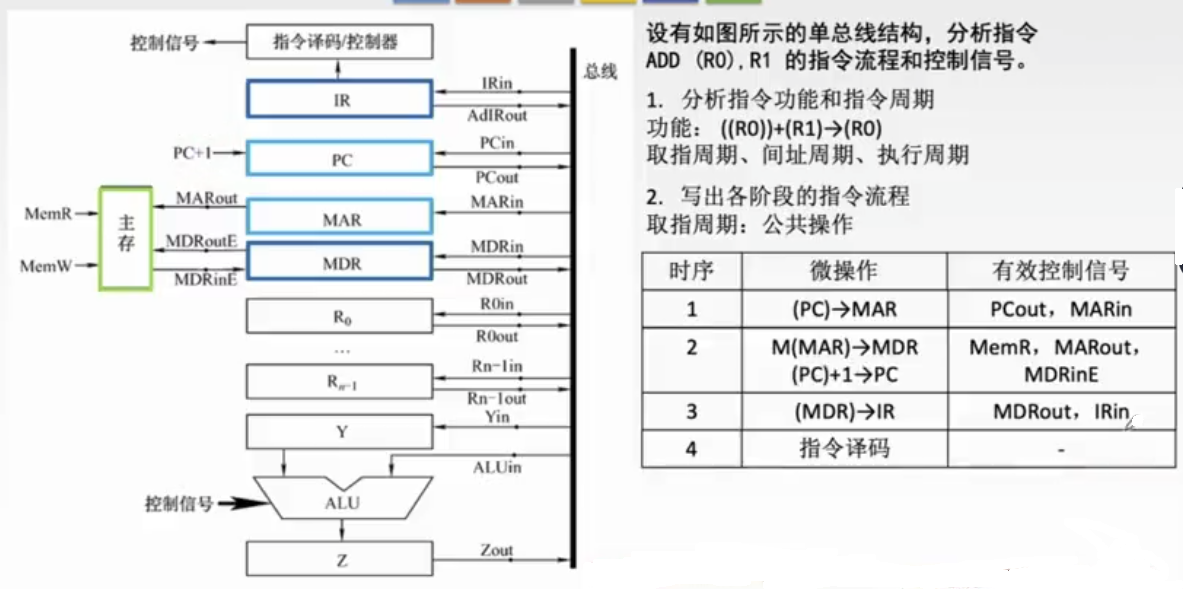

5.3.1 CPU 内部单总线 #

5.3.1 CPU 内部多总线 #

多总线 ALU 可以直接通过总线读取两个操作数, 不再必须暂存寄存器

5.3.1 专用数据通路 #

多路选择器与三态门

5.4 控制器的功能与原理(重点) #

根据指令操作码, 目前的机器周期, 节拍信号和机器状态条件, 判断现在这个节拍下应该发出哪些"微命令"

一条机器指令可以分解为一个微操作序列, 微命令是微操作的控制信号, 微操作是微命令的执行过程

指令是对微指令功能的"封装"

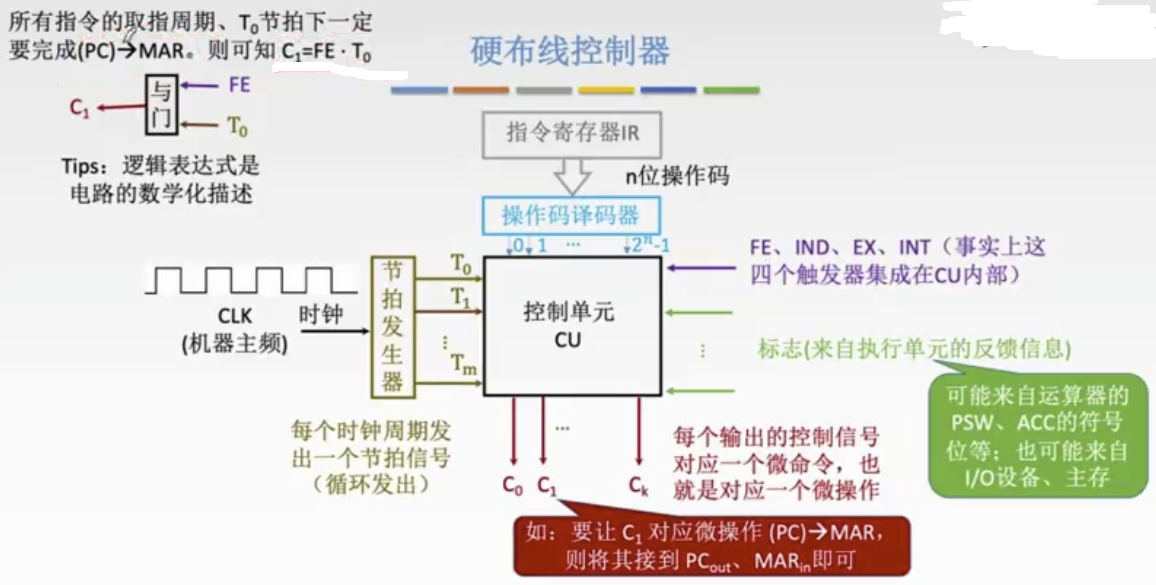

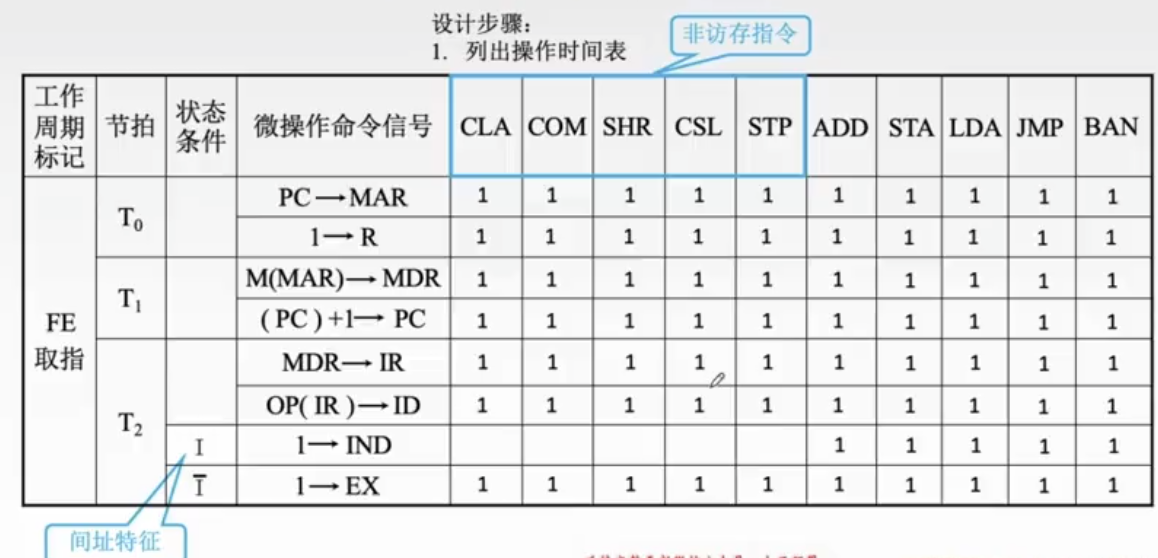

5.4.1 硬布线控制器 #

纯硬件实现

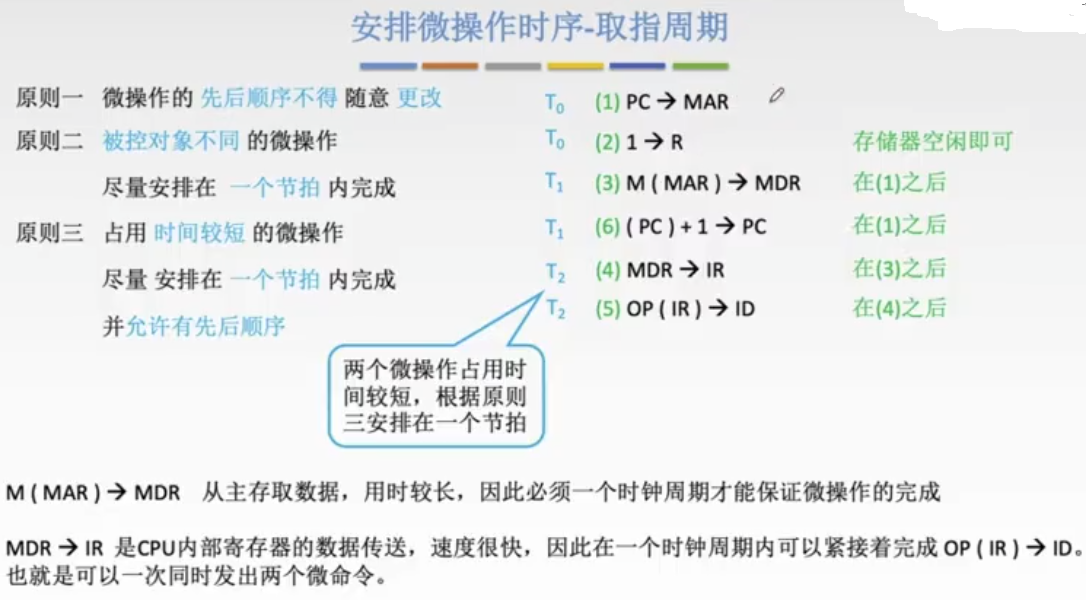

设计硬布线控制器的步骤:

- 分析每个阶段的微操作序列

- 选择 CPU 的控制方式 - 如采用定长机器周期, 一个机器周期安排3个节拍

- 安排微操作时序 - 如何在3个节拍内完成整个机器周期内的所有操作

- 原则1: 微操作的先后顺序不得随意更改(例如某操作必须在某操作后)

- 原则2: 被控对象不同的微操作, 尽量安排在一个节拍内完成

- 原则3: 占用时间较短的位操作尽量安排在一个节拍内完成, 并允许有先后顺序

- 电路设计 - 确定每个微操作命令的逻辑表达式, 并用电路实现

特点:

- 指令越多, 硬件设计越复杂, 因此一般用于 RISC

- 指令扩充困难

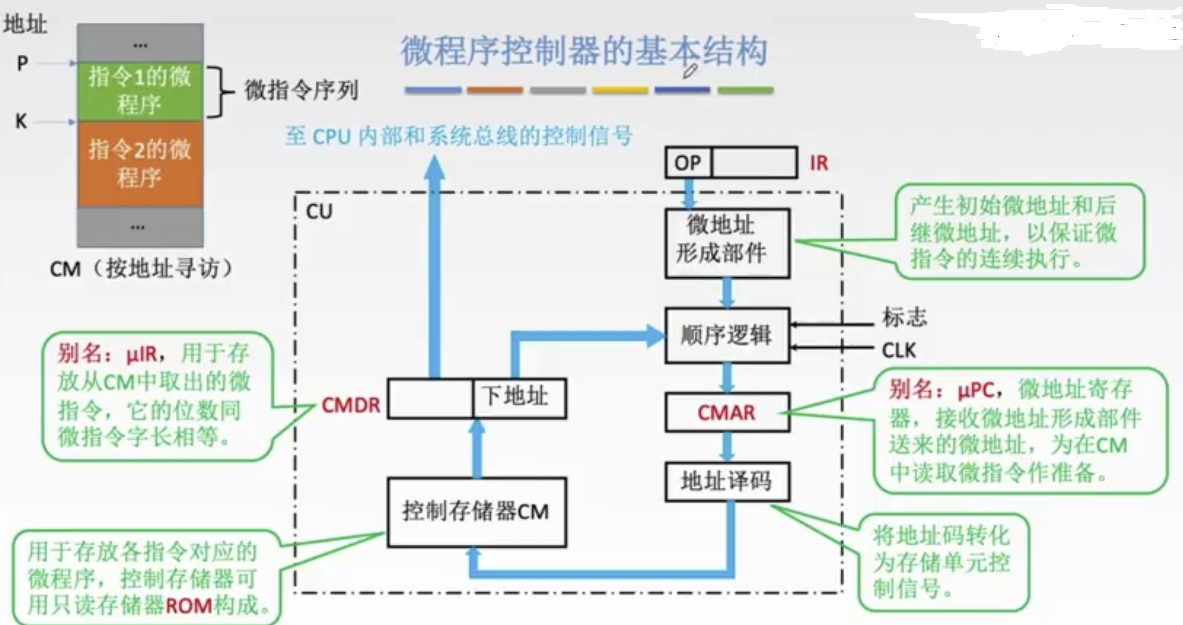

5.4.2 微程序控制器(重点-大题) #

硬件+软件实现

控制存储器 CM: 用于存放各指令对应的微程序, 用只读 ROM 实现

由于取指, 间址和中断周期执行的指令都是通用的, 可以精简实现

5.4.2.1 微指令的设计 #

微指令格式 #

- 水平型微指令 - 一条微指令能定义多个可并行(相容)的微命令

- 微程序短, 集成度高, 执行速度快

- 微指令长, 编写复杂

- 垂直性微命令 - 一条微指令只能定义一个(互斥)微命令, 由微操作码字段规定具体功能

- 微指令短, 简单规整, 易于编写

- 微程序长, 执行速度慢

- 混合型微指令 - 垂直型基础上增加一些不太复杂的并行操作

(水平型)微指令的编码方式(重点) #

目标是保证速度的情况下, 尽量缩短微指令字长

-

直接编码

每一位代表一个微操作命令, 某位为1表示控制信号有效 优点: 简单直观, 可并行, 速度快

缺点: n个微命令就要求微指令的操作字段有 n 位 -

字段直接编码

将互斥的微命令分在同一段, 相容的微命令分在不同段

以一段长度为3位为例, 直接编码可以表示3种命令, 分段编码移码后可以表示 8 种

但通常将 000 保留位不操作, 所以能表示7种互斥的微命令

优点: 可以缩短微指令字长

缺点: 需要经过移码电路再发出微命令, 稍慢

- 字段间接译码

一个字段中的某些微命令需要由另一个字段的某些微命令来解释

(下一条)微指令的地址形成方式 #

- 微指令的下地址字段指出 - 断定方式

- 根据机器指令的操作码形成

- 增量计数器法 - (CMAR) + 1 => CMAR, 适用于后续微指令地址连续的情况

- 分支转移

- 通过测试网络

- 硬件产生的微程序入口地址(如开机第一条微指令的地址)

5.4.2.2 微程序控制单元的设计 #

步骤:

- 分析每个阶段的微操作序列(同硬布线)

- 写出对应机器指令的微操作命令及节拍安排

- 写出每个周期所需要的微操作(参照硬布线)

- 补充微程序控制器特有的微操作:

- 取指周期: (除最后一条)每条微指令结束后

- 根据下地址信息指明接下来要执行的微指令存放地址

- 即 Ad(CMDR) => CMAR

- 取指周期: 最后一条微指令执行完后需要

- 根据指令操作码确定其执行周期的微程序首地址

- 即下一周期(如执行周期)的第一条微指令地址

- OP(IR) => 微地址形成部件 => CMAR

- 执行周期: (除最后一条)每条微指令结束后

- Ad(CMDR) => CMAR

- 取指周期: (除最后一条)每条微指令结束后

- 确定微命令格式

- 根据微操作个数确定编码方式, 进而确定微指令操作控制字段位数

- 根据 CM 中微指令总数, 确定微指令顺序控制字段位数

- 确定微指令字长

- 编写微指令码点(xxx代表xx命令)

5.5 异常和中断机制(重点) #

微指令控制字段分为若干段, 每段经过译码后发出控制信号

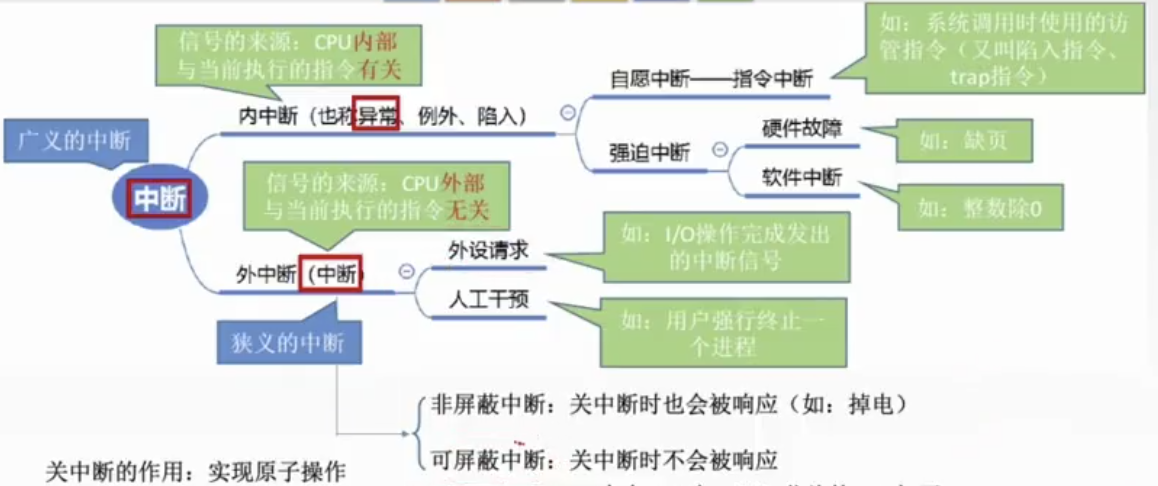

5.5.1 异常和中断的基本概念 #

5.5.2 异常和中断的分类 #

5.5.3 异常和中断的检测与响应 #

5.6 指令流水线(重点-大题) #

5.6.1 指令流水线的基本概念 #

将指令的执行过程分成多个阶段(如取指, 分析, 执行)

指令流水即再上一个指令还未执行完时, 开始执行下一条指令(如第二条执行分析, 第一条执行取指)

根据重叠的阶段数可分为: 一次重叠/二次重叠

性能指标:

- 流水线的吞吐率: 单位时间内流水线完成的任务数量

- 加速比: 完成同样一批任务, 不适用流水线和使用的时间之比

- 效率: 流水线的设备利用率

5.6.2 指令流水线的基本实现 #

流水线设计原则:

- 流水段个数以最复杂指令所用功能段个数为准(x段流水线)

- 流水段长度以最复杂操作所需时间为准 - 各流水段长度相同, 以最长为准

- 因此每个功能段后面都需要添加缓冲寄存器(锁存器)给下个流水段使用

- 可能会导致单条指令执行时间变长

基于流水线批量,规格化的设计思路, 指令集也该具有如下特征:

- 指令长度尽量一致, 简化取指和指令移码; 否则取指未命中缓存, 会频繁导致流水线断流

- 指令格式尽量规整, 尽量保证源寄存器位置相同, 有利于指令未知时可提前取数

- 存取统一使用 Load/Store 指令(RISC即这样实现)

指令流水线的影响因素和分类 #

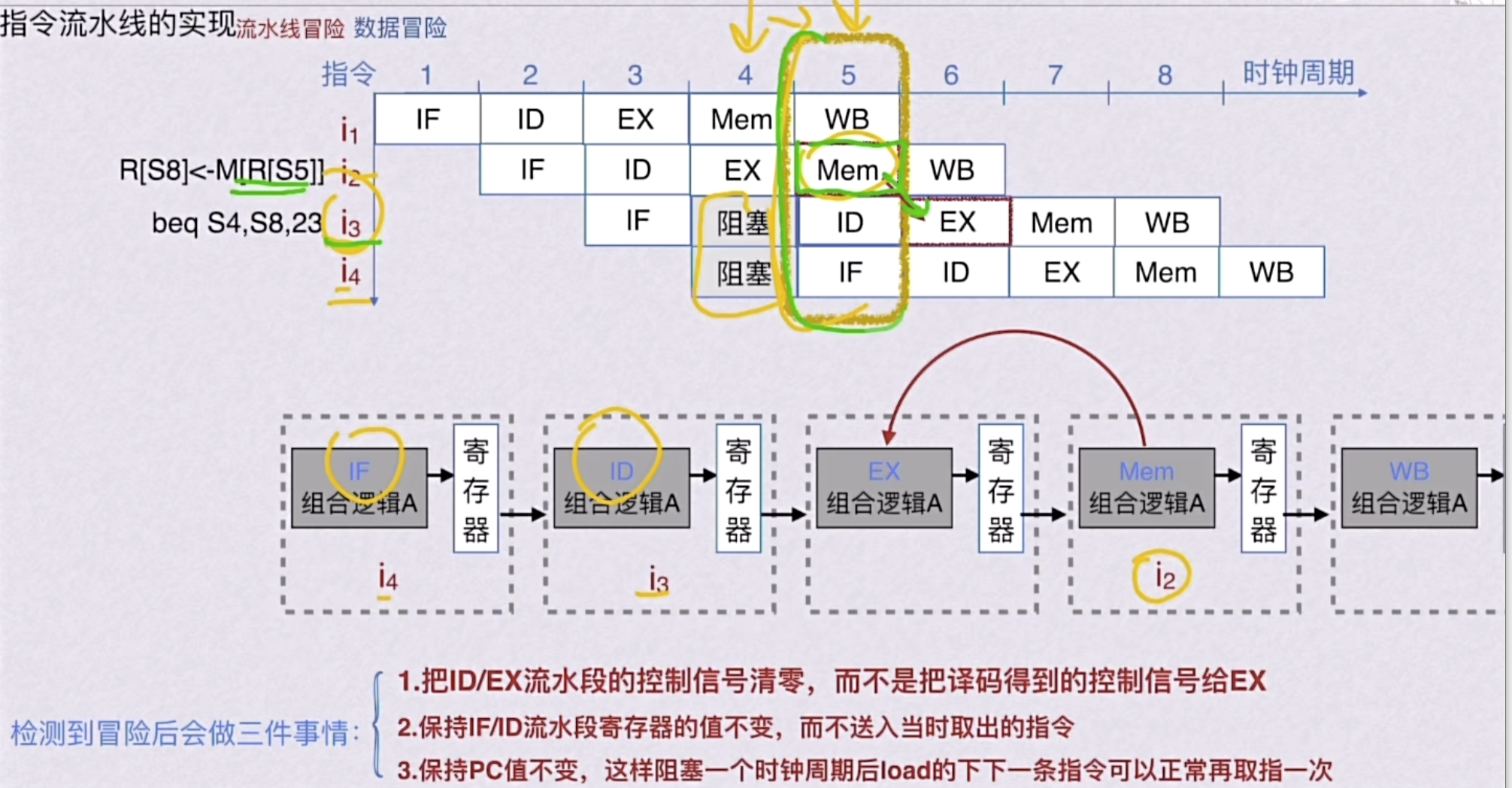

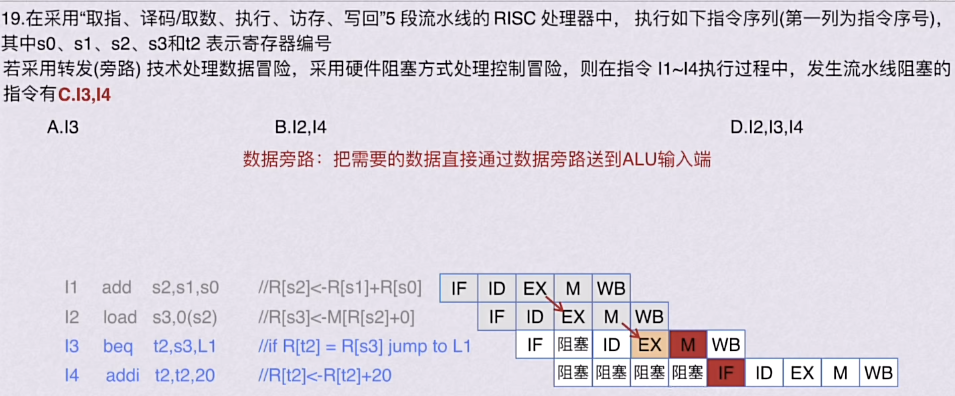

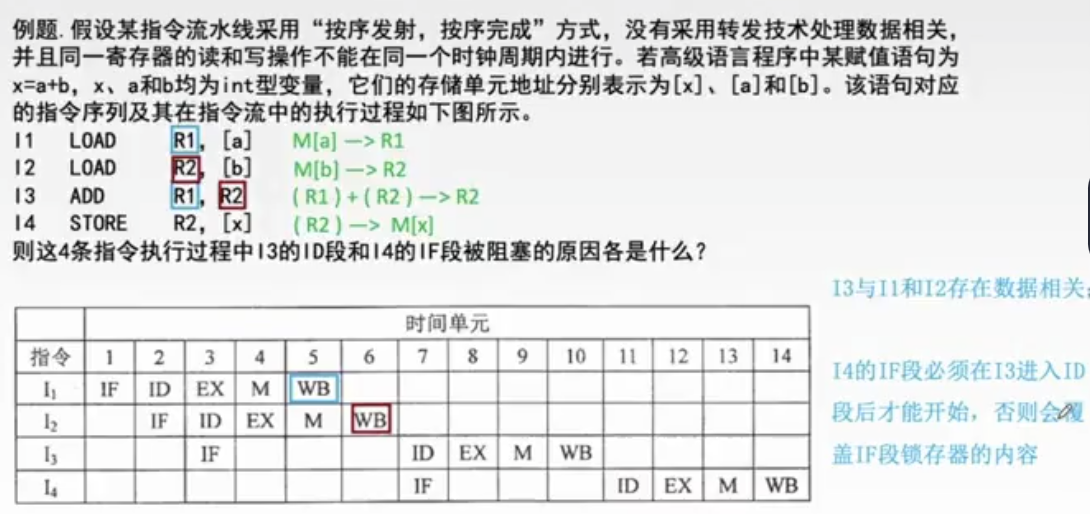

流水线的影响因素 #

- 结构相关(资源冲突) - 多条指令同一时刻争用同一资源形成冲突

- 后一指令暂停一周期

- 资源重复配置

- 数据相关(数据冲突) - 程序中后续指令依赖前面指令的计算结果

- 数据冲突相关指令及其后续指令暂停(硬件阻塞/软件插入NOP)

- 数据旁路(算好直接送到后续指令流水, 不等待写回)

- 增加一个锁存器暂存运算结果, 后续流水线运行直接使用

- load-use 冒险

-

- 编译优化, 调整指令顺序

- 控制相关 - 遇到转移指令或其他改变 PC 的指令从而造成断流

- (转移指令)分支预测 - 简单true/false或者根据历史情况动态预测

- 预取指令, 提前取出成功和不成功的后续指令, 需要增加指令寄存器

- 加快和提前形成条件码

例题:

流水线的分类 #

根据流水线的使用级别:

- 部件功能级 - 流水线专注于完成某种功能如加法操作拆分为流水线

- 处理机级 - 一条指令解释过程拆分, 如拆分为取指译指执行

- 处理机间级 - 宏流水, 每个处理及专门完成一种任务

根据可以完成的功能:

- 单功能

- 多功能

根据同一时间内各段之间的连接方式:

- 静态 - 同一时间内, 流水线各段只能按同一功能的连接方式工作

- 动态 - 同一时间内, 某段实现某种运算, 另一些段进行另一种运算

根据各个功能段之间是否有反馈信号:

- 线性

- 非线性

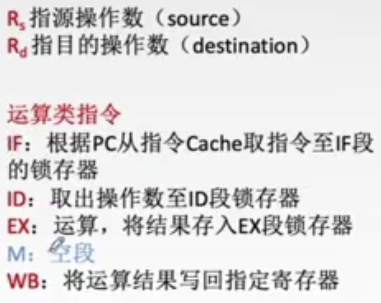

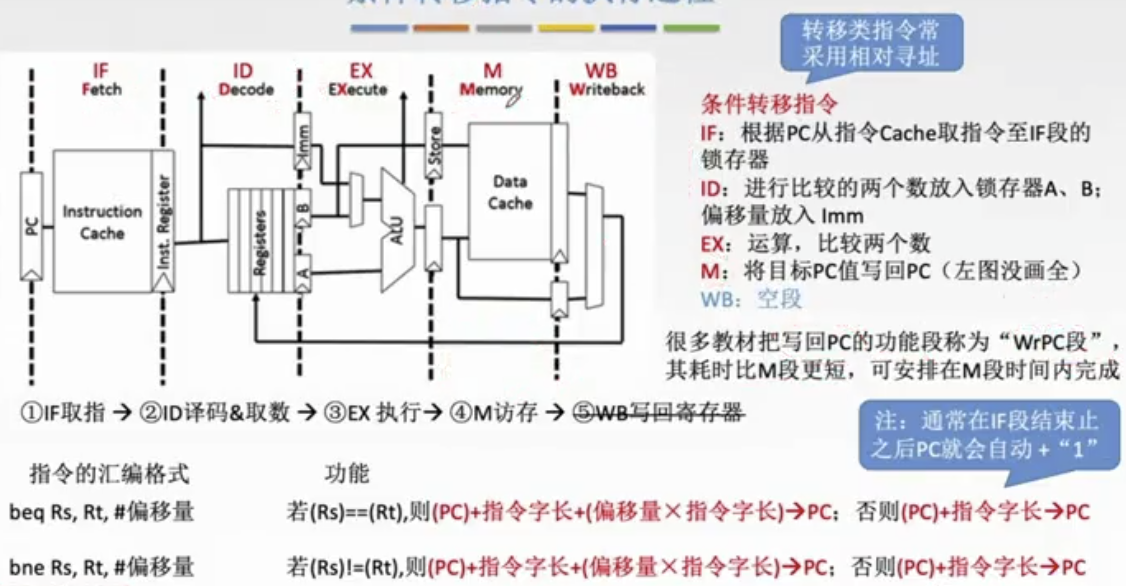

五段式指令流水线(核心重点-大题) #

五段分别为:

- IF(Fetch) - 取指

- ID(Decode) - 译码

- EX(Excute) - 执行

- M(Memory) - 访存

- RISC直接从寄存器取, 无需访问主存

- 大部分情况下都会命中缓存, 否则访问主存会花费一个时钟周期

- WB(Writeback) - 写回寄存器

常考察以下五类指令在流水线中的执行和冲突问题

真题例题:

运算类指令 #

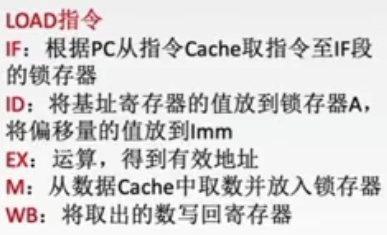

LOAD指令 #

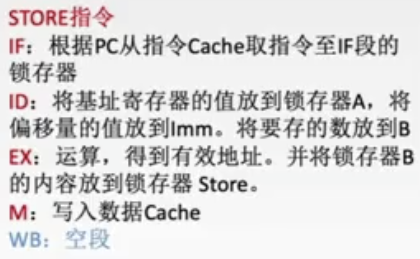

STORE指令 #

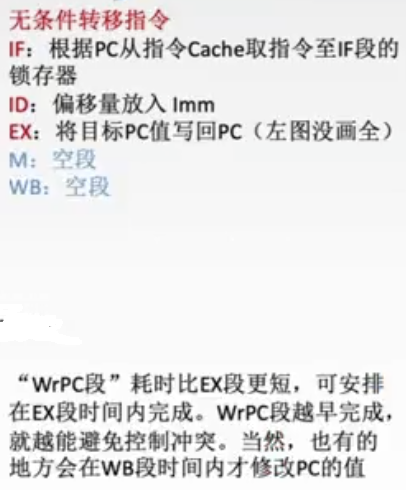

条件转移指令 #

转移类指令常采用相对寻址(PC + 偏移量)

无条件转移指令(jmp) #

5.6.3 结构冒险, 数据冒险和冒险控制的处理 #

5.6.4 超标量和动态流水线的基本概念 #

超标量流水线: 每个时钟周期并发多条独立指令(每个指令又开启一条流水线)

5.7 多处理器基本概念 #

5.7.1 SISD, SIMD, MIMD, 向量处理器的基本概念 #

5.7.2 硬件多线程的基本概念 #

5.7.3 多核处理器的基本概念 #

5.7.4 共享内存多处理器(SMP)的基本概念 #

- CPU 的功能与基本结构

- 指令的执行过程(可能出大题)

- 指令周期

- 取值周期

- 间址周期

- 执行周期

- 中断周期

- 数据通路(基本功能, 三种方式的基本结构)

- 控制器的功能与原理

- 结构与功能

- 两类控制器

- 硬布线控制器

- 微程序控制器

- 异常和中断机制(分类, 响应过程)

- 指令流水线

- 性能指标

- 影响因素

- 分类

- 多并发技术

- 五段式流水线(重中之重, 大题)

- 多处理器的基本概念

6. 总线 #

6.1 总线的基本概念 #

总线的: 一组能为多个部件分时共享的公共信息传送线路

- 分时 - 同一时刻只允许一个部件向总线发送信息

- 共享 - 多个部件可以同时从总线上接受相同的信息

总线按功能分类:

- 片内总线 - 芯片内部的总线, 如 CPU 与 ALU 与寄存器直接

- 系统总线 - 计算机内各部件(CPU, 主存, IO接口)之间互相连接的总线

- 数据总线

- 传输各功能部件间的数据信息, 双向传输

- 双向传输

- 位数与机器字长, 存储字长相关

- 地址总线

- 指出数据总线上元数据或目的数据所在主存单元或IO端口的地址, 单向传输

- 位数与主存地址空间的大小相关

- 控制总线

- 传输控制信息, 包括CPU送出的控制命令和其他设备返回CPU的反馈信号

- 数据总线

- 通信总线 - 与其他计算机系统之间通信

6.2 总线的组成和性能指标 #

6.2.1 总线结构(重点) #

- 单总线结构

- 一套, 而非一根, 数据/地址/控制总线还是完整的

- CPU, 主存, IO 设备都挂在该总线上

- 不支持并发, IO 设备速度慢会拖累总线整体速度

- 双总线结构

- 分为主存总线和IO总线, 主存总线新增加通道连接IO总线

- 分级缓存思想

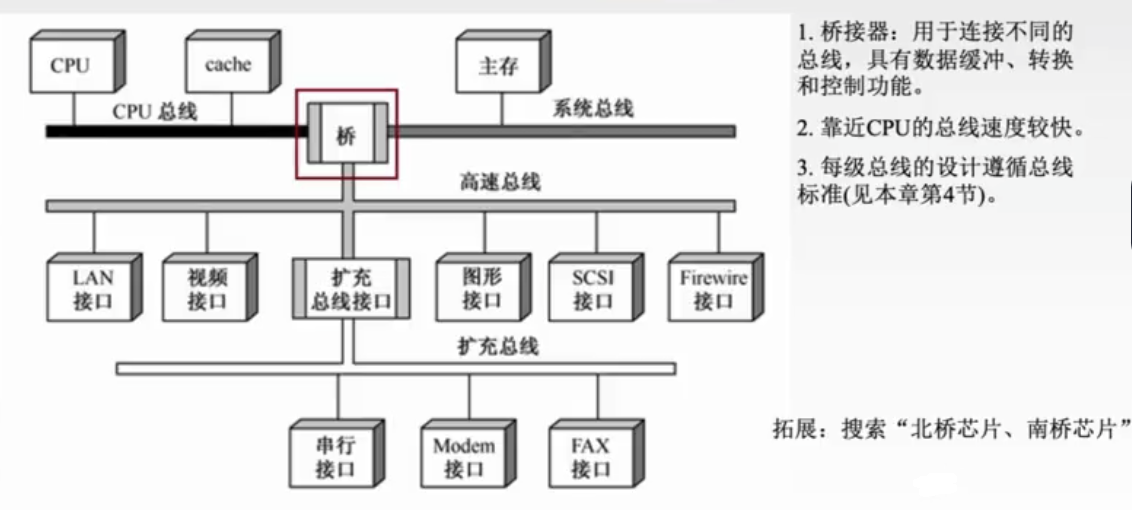

- 三总线结构

- 区分高/低速IO设备, 进一步细化分级缓存, 提高了 IO 性能

- 缺点: 三条总线只能同时有一个工作, 效率较低

-

- 四总线结构(扩展知识不考察)

- 现代计算机结构

-

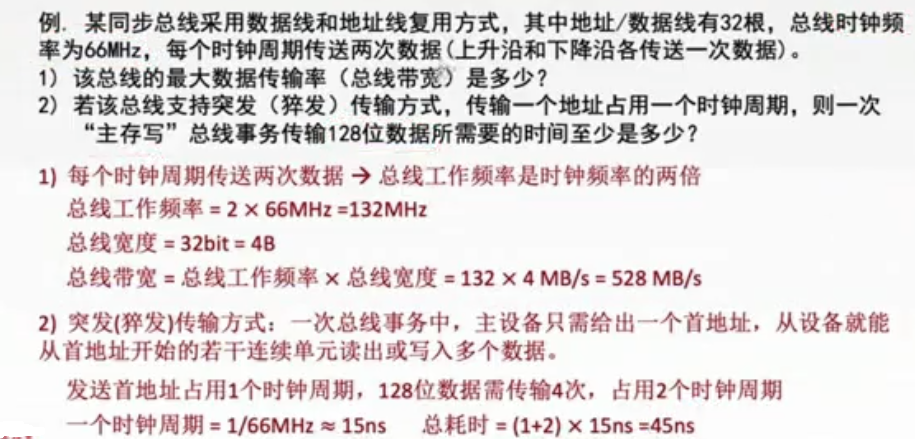

6.2.2 性能指标 #

- 总线的传输周期(总线周期) - 一次总线操作所需的时间(申请/寻址/传输/结束)

- 总线的时钟周期 - 机器的时钟周期

- 现代计算机也可能由桥接器提供, 不考察

- 总线的工作频率 - 总线周期的倒数, 即一秒内传送几次数据

- 总线的时钟频率 - 时钟周期的倒数

- 总线宽度(总线位宽) - 能够同时传输的数据位数, 通常指数据总线根数

- 总线带宽 - 单位时间可传输数据的位数 = 工作频率 x 位宽

- 指最高数据速率,非有效信息速率

- 总线复用 - 如用同一组线分时传输地址和数据信息

- 信号线数 - 数据/地址/控制3种总线数的总和

例题 #

6.3 总线事务和定时 #

6.3.1 总线仲裁 #

解决多个(主)设备同时竞争总线控制器的问题

集中仲裁(重点) #

- 链式查询 - 由总线控制器发出总线允许信号(BG)

- 离的越近的设备越先接收到信号并发出总线忙信号(BS)

- 优先级固定, 电路故障敏感, 距离远的设备可能长期获取不到控制权

- 计数器定时查询

- 用计数器控制总线使用权(计数器值 === 设备地址)

- 多了一组设备地址线, 少了一根总线响应线BG

- 可以通过调整计数器初始值调整优先级, 电路故障不敏感

- 线束增加, 控制复杂

- 独立请求

- 每个设备都有总线请求线BR和总线允许线BG, 总线控制器负责排队

- 响应快, 控制优先级灵活

- 控制线多, 2n(BR + BG) + 1(BS) 条

分布仲裁 #

每个主模块都有自己的仲裁器和仲裁号

请求总线时, 将自己的仲裁号发送到共享的仲裁总线上

根据仲裁号的优先级响应保存在仲裁总线上, 并撤销其它仲裁号

6.3.2 总线操作 #

总线传输的4个阶段:

- 申请分配阶段(传输请求 + 总线仲裁)

- 寻址阶段 - 本次主设备发出要访问的从设备的地址和有关命令

- 传输阶段

- 结束阶段 - 主设备撤除自己在系统总线上的信息, 让出总线使用权

6.3.3 总线定时 #

控制数据传输的时间节点

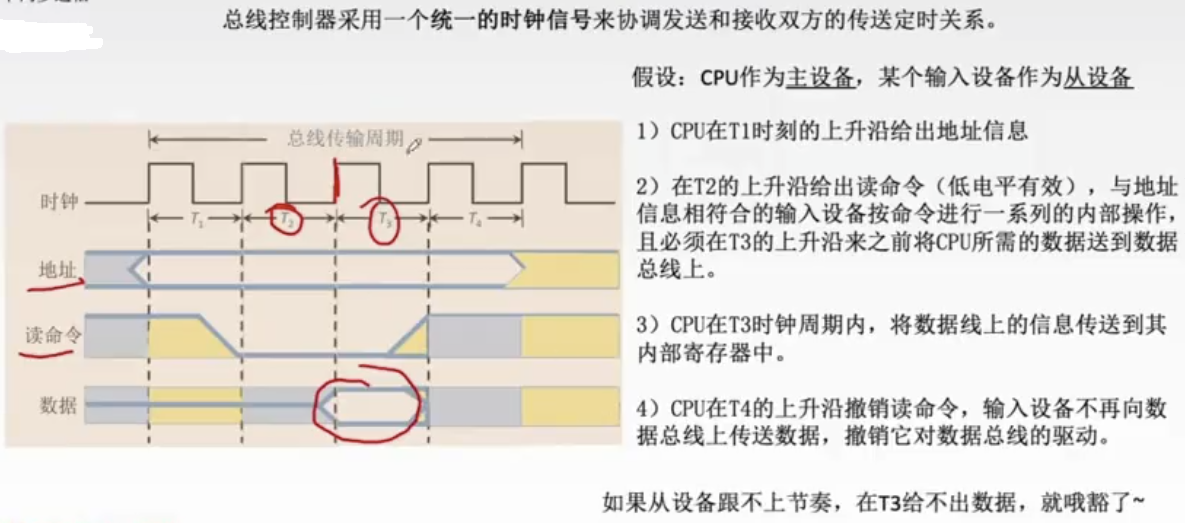

同步定时方式 #

强制在始终周期的节点进行特定操作, 简单快, 但可靠性差

例如: 发送方在时钟前沿发信号; 接收方在时钟后沿判断识别

适用总线长度短或各部件存取时间相近的系统

异步定时方式(重点) #

依靠握手信号实现定时控制, 主设备发出"请求"信号, 从设备发出"回答"信号

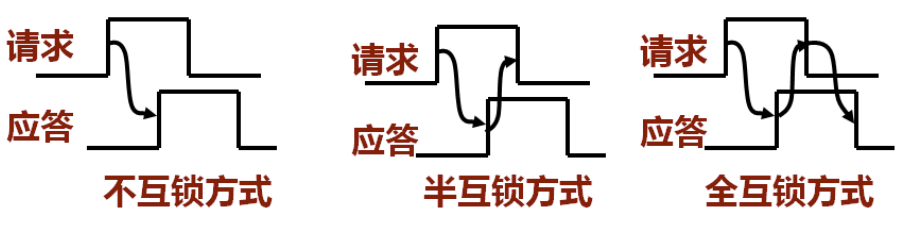

根据"请求"和"回答"信号的撤销是否互锁, 又分为(速度依次变慢, 可靠性依次提升):

- 不互锁方式

- 主设备请求后, 不等回答; 一段时间后, 撤销请求信号

- 从设备收到请求后, 发出回答; 一段时间后, 撤销回答信号

- 半互锁方式

- 主设备请求后, 等到回答后, 才能撤销请求信号

- 从设备收到请求后, 发出回答; 一段时间后, 撤销回答信号

- 全互锁方式

- 主设备请求后, 等到回答后, 才能撤销请求信号

- 从设备收到请求后, 发出回答; 收到撤销请求后, 才能撤销回答

需要总线周期长度可变, 可以保证速度相差较大的部件可靠地进行信息交换

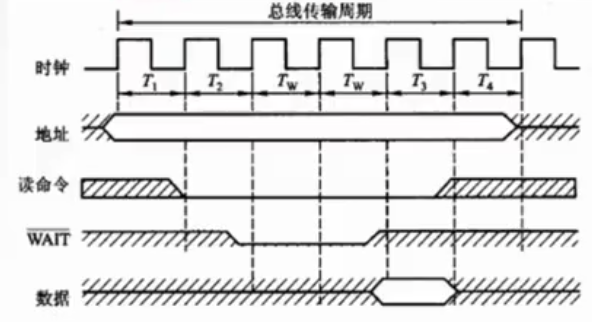

半同步通信 #

在统一时钟的基础上, 增加一个等待信号

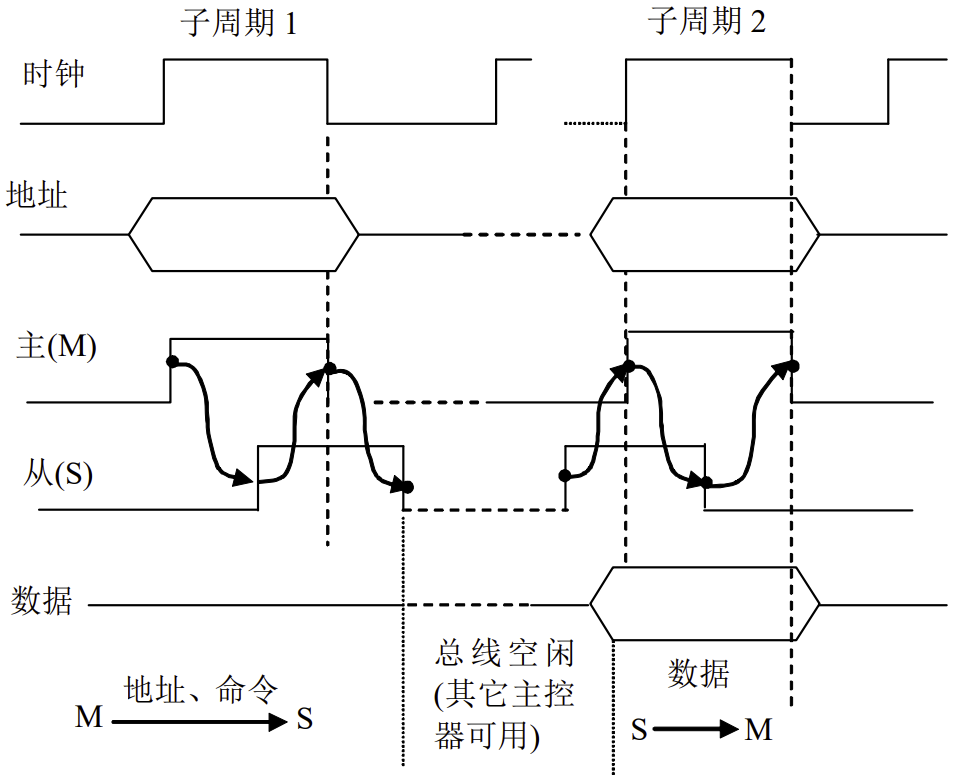

分离式通信 #

可以观察到之前的通信方式共同点:

- 主模块发地址和命令 - 使用总线

- 从模块准备数据 - 不使用总线

- 从模块向主模块发数据 - 使用总线

为了利用第二阶段, 分离式通信将一个总线周期分为两个子周期:

- 主模块申请占用总线, 使用完后立即放弃总线的使用权

- 从模块准备好数据后, 申请占用总线(需要改造), 将信息传送到总线上

6.4 总线标准 #

了解即可

涉及哪些方面:

- 并行/串行

- 几根数据线? 几根地址线? 是否复用

- 总线仲裁方式

- 总线定时方式

- 总线工作频率

- 电气特性…

各厂商协商好后, 从而发起制定标准

根据总线在计算机中的位置, 可分为:

- 系统总线:与 CPU 直连, 如 CPU 与北桥芯片, CPU 与主存

- ISA 并行总线, 1984提出

- EISA 并行总线, 1988提出, ISA 基础上增加位宽

- 局部总线: 通常由(高速)北桥芯片控制, 连接重要的(高速)硬件, 如显卡

- VESA 并行总线

- PCI 并行总线

- AGP 并行总线, PCI 扩展专门用于显卡

- PCI-E - (2001提出)现行使用统一总线标准, PCI 升级而来, 连接显卡, 网卡等

- 点对点串行传输

- 设备/通信总线: 通常由(低速)南桥芯片控制, 连接 IO 与外部计算机设备

- RS-232C 串行

- SCSI 并行

- PCMCIA 并行

- USB - 连接外部设备的通用串行总线

- 可供电, 根据压差来确定 bit 数据, 差模信号抗干扰能力强, 可高频率运行

- IDE - 并行总线, 硬盘/光驱接口

- SATA - 串行高级技术附件, 硬盘接口规范

串行逐渐替代并行的原因:

并行总线:

- m 根线传输 m 个比特, 高低电平表示1/0, 定时同步

- 线间干扰导致频率不能太高

- 各条线不能有长度差, 工艺难度大

串行总线: - 两根线每次传送1个比特, 差模信号表示1/0, 异步定时

- 频率较高

- 基于包传输(如xx比特为一个包), 可以多个数据通路分别串行传输多个包(如PCIE x 4/8)

7. 输入输出系统 - I/O #

操作系统IO部分更多注重软件, 机组内侧重硬件

7.1 基本概念 #

I/O 系统组成:

- I/O 软件 - 驱动/用户程序等, 通常采用 I/O 指令和通道指令实现信息交换

- I/O 指令格式: 操作码(CPU命令接口) + 命令码(接口命令设备) + 设备码

- I/O 硬件 - 外部设备, 设备控制器和接口, I/O 总线等

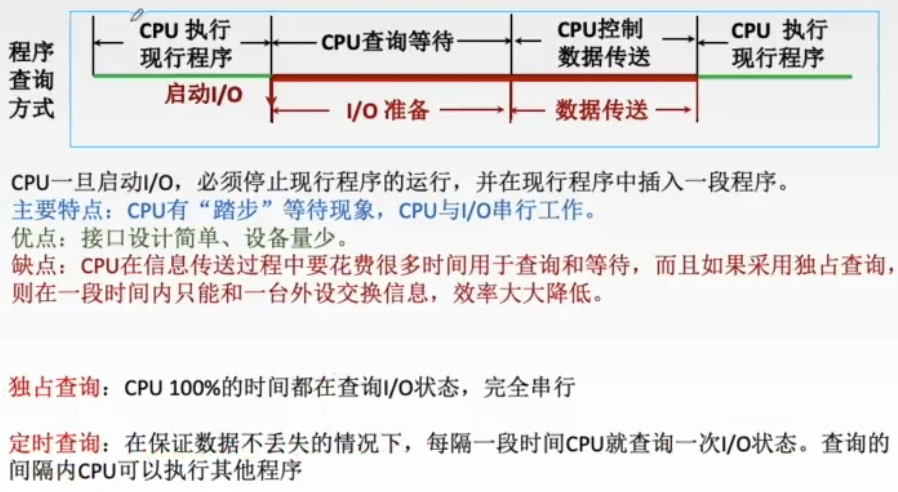

7.1.1 I/O 控制方式 #

- 程序查询 - CPU 轮询检查 I/O 接口内的状态寄存器, 根据状态交互

- 程序中断 - I/O 设备就绪时向 CPU 发起中断请求, CPU 响应后继续交互

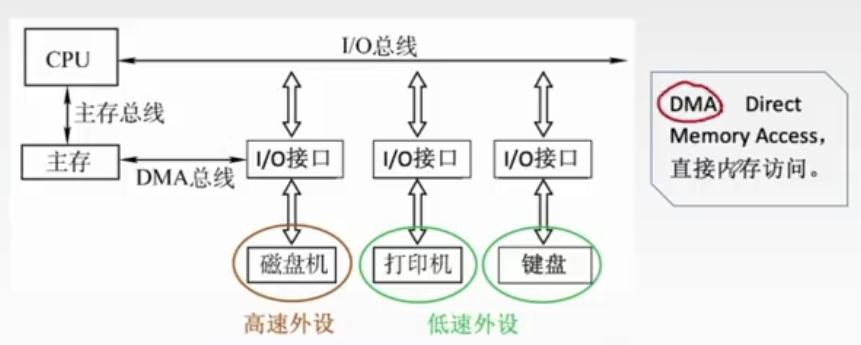

- DMA - 主存和 I/O 设备直连

- 通道方式 - 类似南北桥, 每个通道外挂若干设备, I/O 由通道执行

1,2 适用于慢速设备(避免频繁检查/中断); 3,4 适用于快速设备

参考三总线结构

7.1.2 外部设备 #

输入设备 #

输入设备: 键盘, 鼠标

输出设备 #

输出设备: 显示器, 打印机

显示器主要参数:

- 屏幕大小: 对角线长度

- 分辨率: 横/纵像素乘积

- 灰度级: 黑白显示器能显示像素点的亮暗差别; 彩色显示器则表现为颜色的不同

- 刷新频率: 光点只能保持极短的时间消失, 必须定时重新扫描显示

- 显示存储器VRAM - 显存(重点)

- 为了提高刷新图像的"信号?", 将一帧图像(最小容量)储存在刷新存储器中

- VRAM 容量 = 分辨率 * 灰度级位数

- VRAM 带宽 = 分辨率 * 灰度级位数 * 帧率

- 现代计算机中(不考仅扩展)

- 显存除了保存当前显示帧的缓存, 还会用于保存即将渲染的图像数据(不考虑GPU)

- 集成显卡划分一片内存作为显存, 独立显卡有独立的显存

显示器类型:

- CRT 阴极射线管显示器

- LCD

- LED

- OLED

外存储器 #

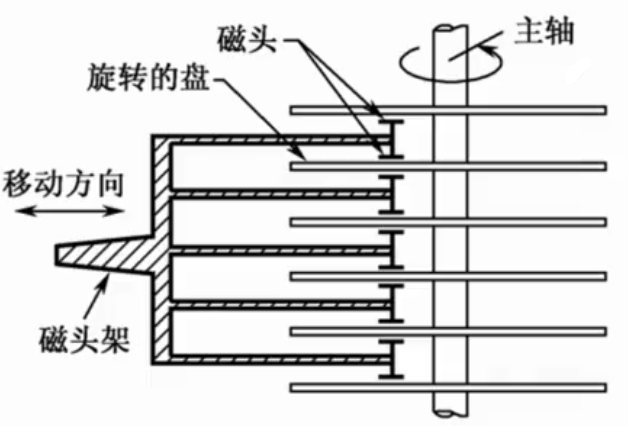

磁盘设备的组成 #

- 存储区域 - 一块硬盘多个盘面, 每个盘面多个磁道, 每个磁道多个扇区(最小单位)

- 磁头数 - 通常一个盘面对应一个磁头

- 柱面数 - 相同的磁道组成了柱面, 磁道数即柱面数

- 扇区数

- 硬盘存储区 - 有磁盘驱动器, 磁盘控制器和盘片组成

- 磁盘驱动器

- 磁盘控制器 - 接口, 如 IDE, SATA

现代磁盘大多是双面存储的, 示意图:

磁盘的性能指标 #

- 容量: 非格式化容量 < 格式化容量

- 记录密度

- 道密度 - 沿磁盘半径方向上, 单位长度的磁道数, xx道/cm

- 位密度 - 磁道单位长度上能记录的二进制信息量, 600bit/cm

- 所有磁道记录的信息量相等, 因此越靠内位密度越高

- 面密度 = 道密度 * 位密度

- 平均存取时间(重点)

- 寻道时间(磁头移动到目的磁道)

- 旋转延迟时间(定位到所在扇区)

- 传输时间

- 数据传输率 - 单位时间向主机传送数据的字节数

- 假设磁盘转数 r(转/秒), 每条磁道容量 N 个字节

- 数据传输率 = r * N

磁盘地址 #

依次为:

- 驱动器号 - 一台电脑可能有多个硬盘

- 柱面(磁道)号 - 移动磁头臂寻道

- 盘面号 - 激活某个磁头

- 扇区号 - 旋转将特定扇区划过磁头

磁盘阵列 RAID #

分类如下(越往后可靠性越高):

- RAID0 - 无冗余和无校验的磁盘阵列

- 类似低位交叉编址扩展

- RAID1 - 镜像磁盘阵列

- 双备份, 空间利用率减半

- RAID2 - 采用纠错的海明码的磁盘阵列

- 逻辑上连续的 bit 物理上分散存储在各个盘中

- 4bit信息位 + 3bit海明校验位, 可纠正一位错

- RAID3 - 位交叉奇偶校验的磁盘阵列

- RAID4 - 块交叉奇偶校验的磁盘阵列

- RAID5 - 无独立校验的奇偶校验的磁盘阵列

7.2 I/O 接口(I/O控制器) #

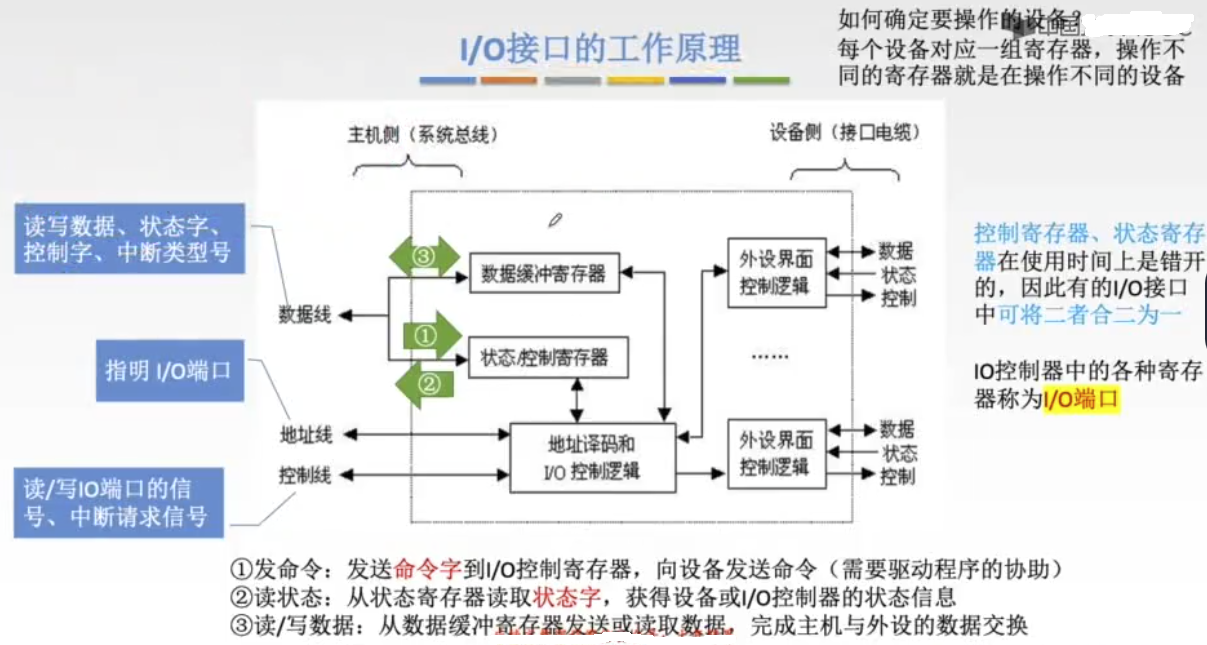

7.2.1 功能和基本结构 #

功能:

- 实现主机和外设的通信联络控制

- 地址译码和设备选择

- 数据缓冲

- 信号格式的转换 - 串/并转换, 模/数转换等

- 传送控制命令和状态信息 - 例如接受外部设备"准备就绪"的状态至状态寄存器

基本结构(注意状态/控制共用一个寄存器):

7.2.2 端口及其编址 #

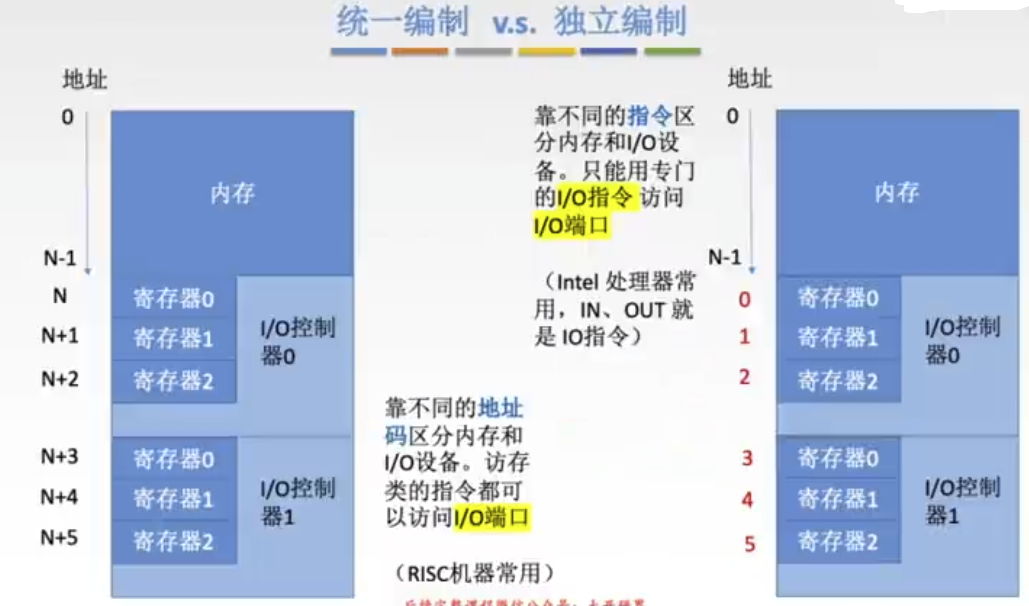

编址方式:

- 统一编址(存储器映射)

- 无需 I/O 指令, 统一访存指令就可以访问 I/O 端口

- I/O 地址占用主存编址空间, 使可用内存容量变少

- 地址译码速度变慢

- 独立编址

- 使用专用 I/O 指令, 需要 CPU 增加额外控制信号

- 不占用主存空间

- I/O 端口地址位数少, 译码快

统一编制(存储器映射方式):

7.3 I/O 方式(重点) #

7.3.1 程序查询方式 #

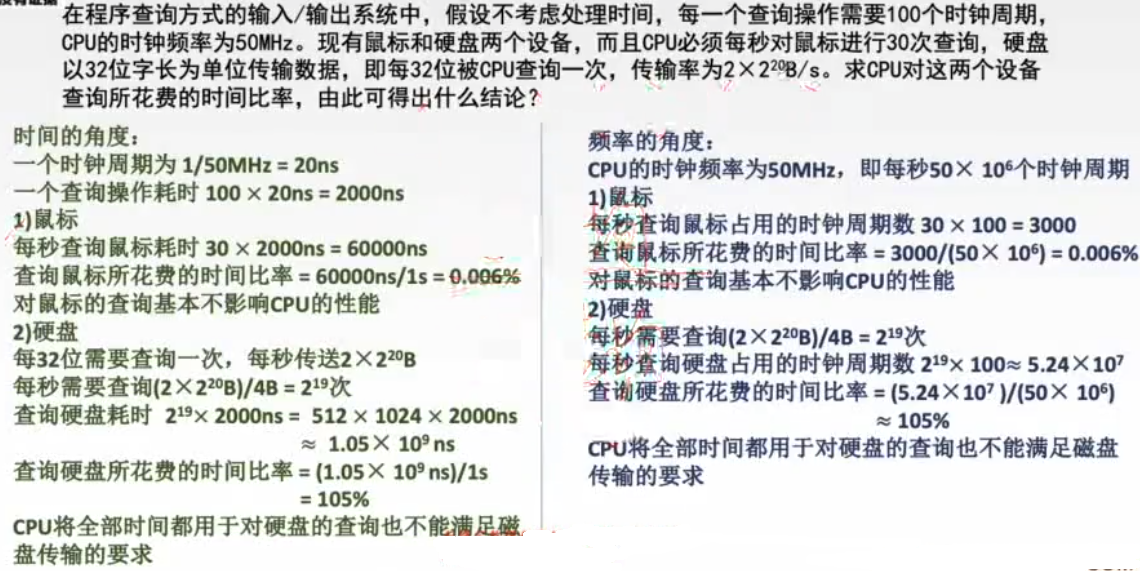

例题:

7.3.2 程序中断方式(重点) #

中断和函数调用的区别: 函数调用仍然归属于当前进程, 中断后控制器转移给别的进程

中断分类 #

本章讨论的均为 I/O 设备的外设请求中断, 即可屏蔽的中断

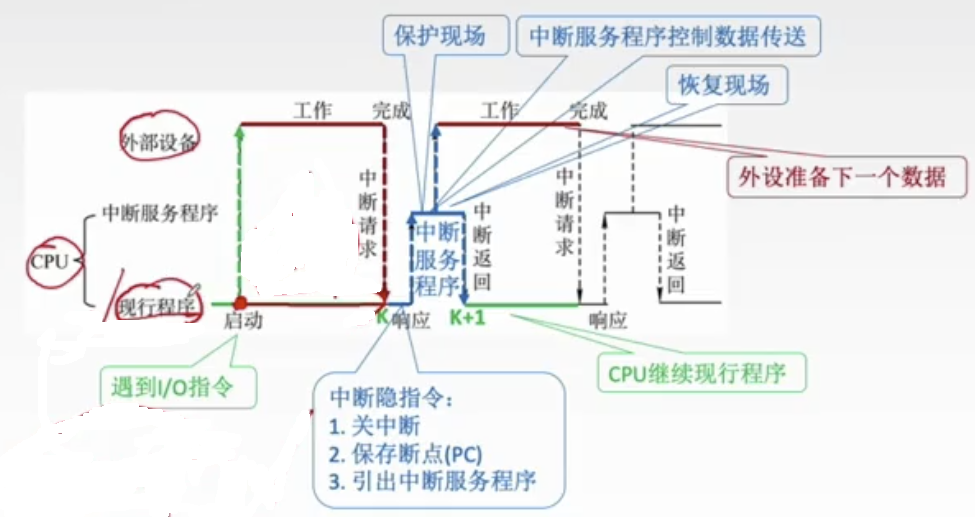

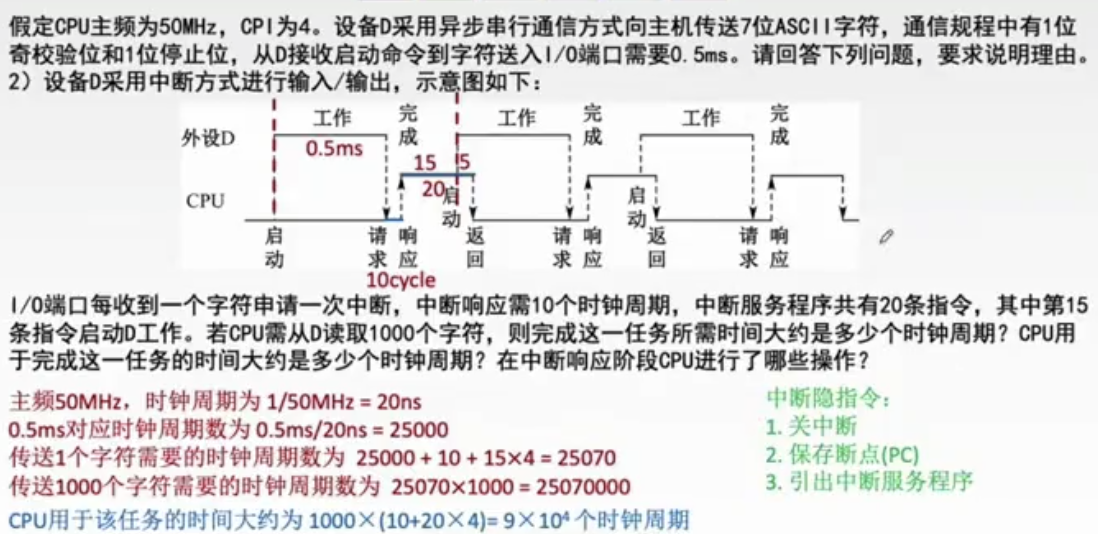

程序中断工作流程(重点) #

- 中断请求

- 每个中断源设置中断请求标记触发器 INTR, 其发出的属于可屏蔽中断

- NMI 信号发出的是不可屏蔽中断, 优先级最高

- 中断判优

- 硬件实现 - 硬件排队器(例如高优先级位高电平会通过非门给其它位一个0信号)

- 软件实现 - 根据优先级按位检查

- 中断响应

- 执行中断隐指令 - 硬件实现, 非指令系统中真正的指令

- 关中断

- 保存断点(PC值存入堆栈), 以便后续中断结束返回继续执行

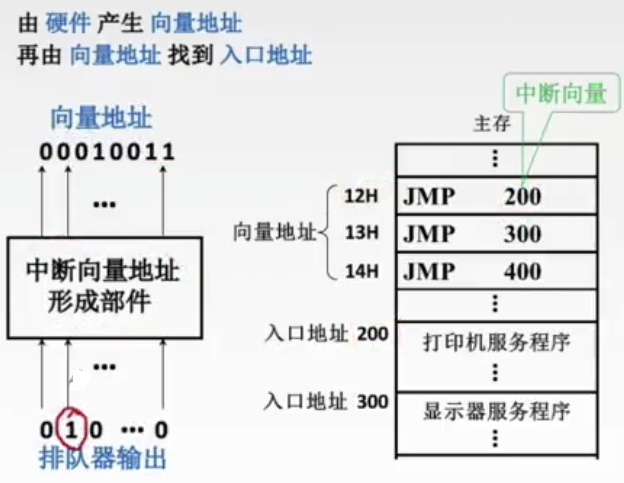

- 引出终端服务程序, 取出中断服务程序入口地址并存入 PC, 如何确定地址?:

- 软件查询法

- 硬件向量法

- 根据排队器输出的信号生成向量地址(中断类型号)

- 根据终端类型号去中断向量表查表, 得到中断程序入口地址的指针

-

- 执行中断隐指令 - 硬件实现, 非指令系统中真正的指令

- 中断处理过程(各计算机实现不同, 这里可能由隐指令完成的过程也整体列出)

- 保护现场

- 关中断

- 保存断点(各变量, 如保存 ACC 中值)

- 中断服务(设备服务)

- 恢复现场

- 中断返回

- 保护现场

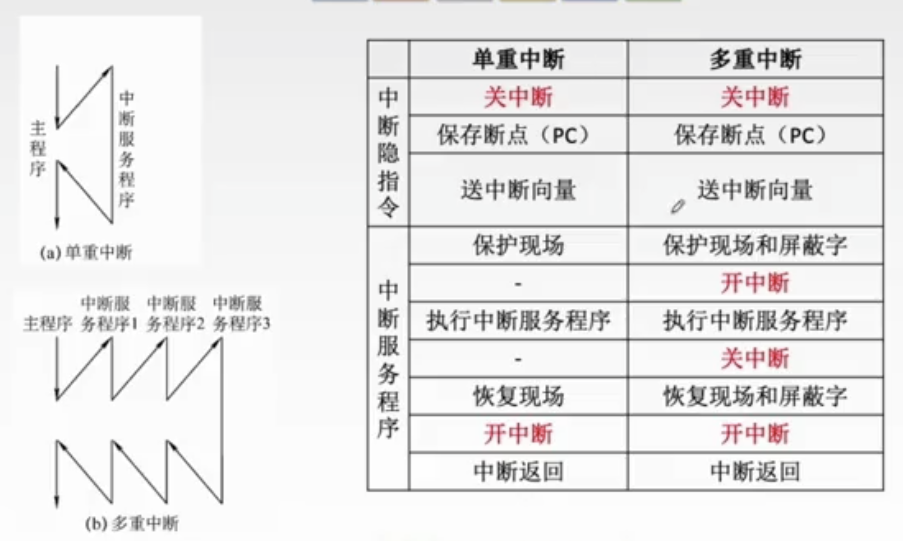

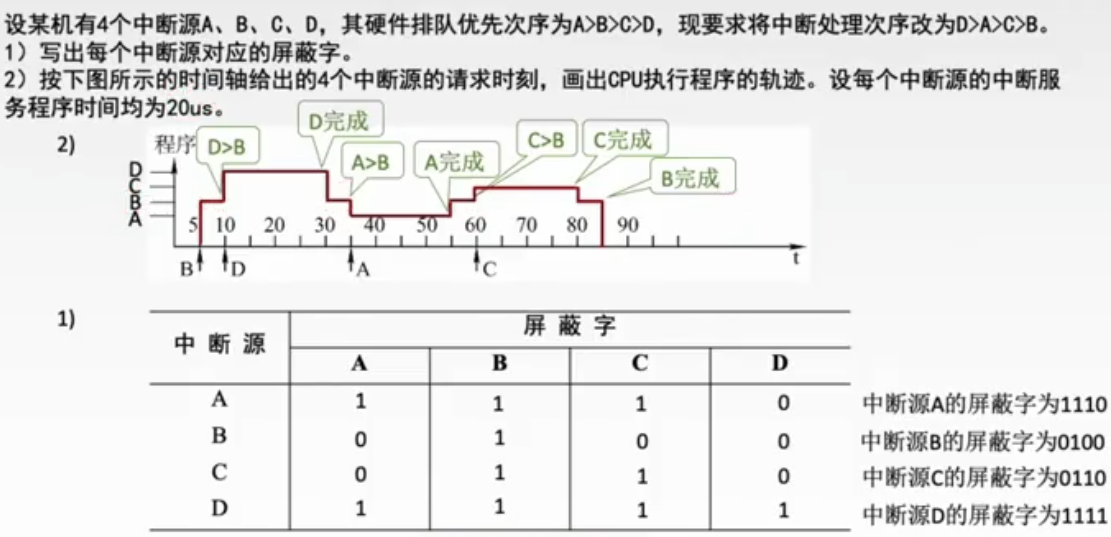

多重中断 #

要实现多重中断, CPU 需要支持优先级高的中断源有权中断优先级低的中断源

因此需要实现中断屏蔽技术:

- 每个中断源都有一个屏蔽触发器, 1表示屏蔽中断请求

- 所有触发器组合在一起称为屏蔽字寄存器

- 每个中断源对应一个屏蔽字, 处理该中断时, 屏蔽寄存器中内容为对应的中断字

- 屏蔽字 1 越多即优先级越高(至少要能屏蔽自身的中断, 因此至少有一个1)

例题:

CPU占用 #

CPU占用流程图:

例题:

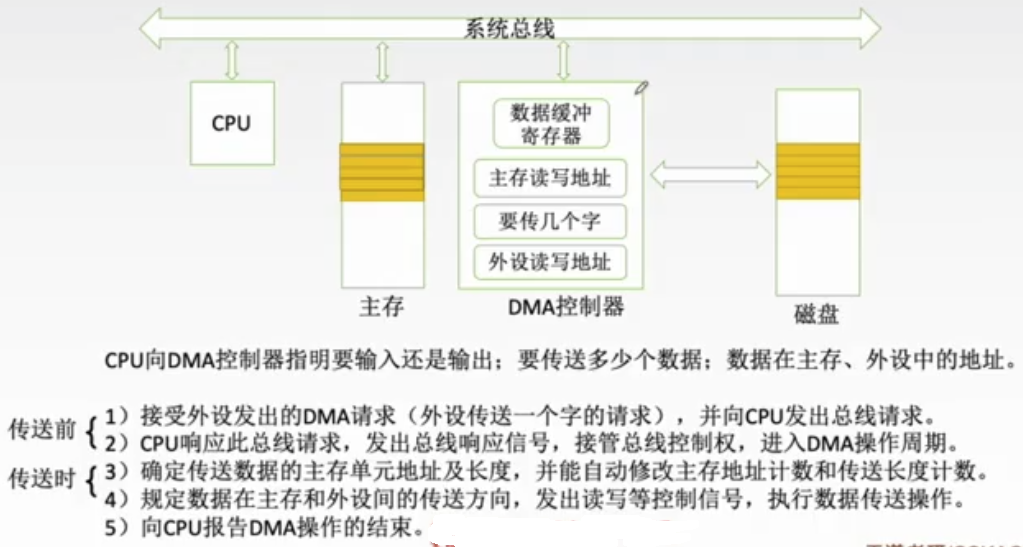

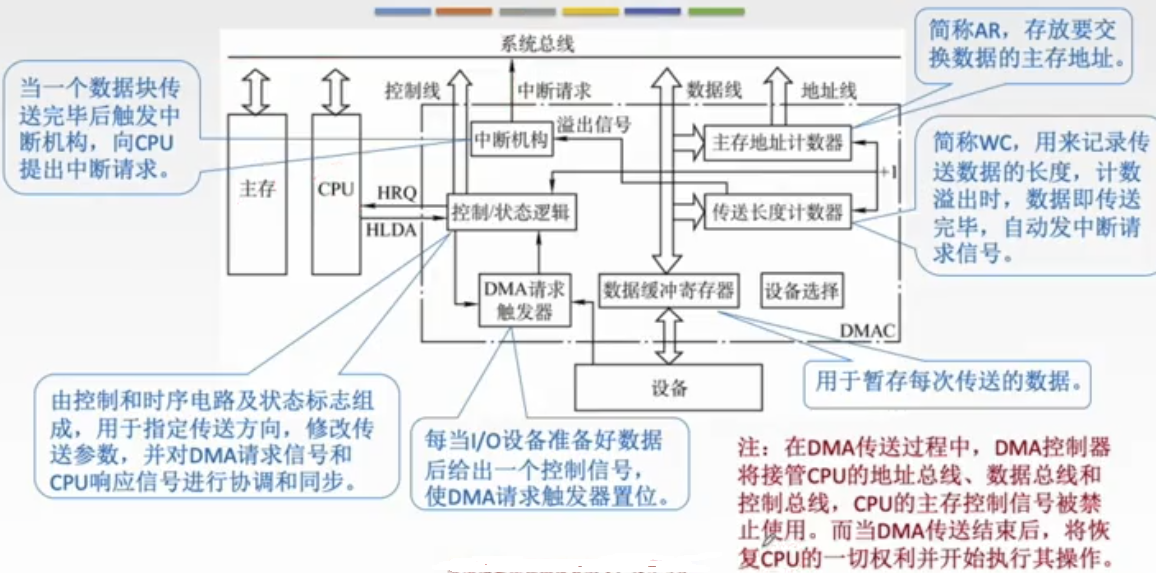

7.3.3 DMA 方式 #

通常用来控制块(以块为单位读写)设备, 如磁盘

DMA 结构 #

DMA 简要流程和建议结构:

DMA 结构图:

DMA 传送过程(重点) #

- 预处理

- CPU 向 DMA 控制器指明接下来要读写的数据存放在主存中的起始地址 => AR

- 指明设备的读写地址 => DAR

- 指明要传送多少数据 => WC

- 启动 I/O 设备

- 数据传送

- 以读取外设数据为例, 设备将数据写入数据缓冲寄存器 => DR

- 写满后向 DMA 控制器请求发送 DMA 请求

- DMA 申请总线控制权 => HRQ, CPU 统一申请则返回信号 => HLDA

- DMA 将数据 => 总线 => 主存

- 此阶段完全由 DMA 控制, CPU 可继续执行任务

- 后处理

- 中断服务程序(如传送长度计数器WC将要溢出, 说明已经缓冲了一个块的数据需要写入一次)

- DMA 结束处理

- 继续执行主程序

DMA 传送方式 #

数据传送阶段 DMA 需要申请总线控制权以读写主存, CPU 此时可能也在使用

此时分三种方式使用主存:

- 停止 CPU 访问 - 不利于 CPU 利用率

- 交替访存

- 将 CPU 周期分为两个子周期, 交替访问主存

- 适用 CPU 工作周期比主存周期长的情况

- 周期挪用(周期窃取)

- 如果 CPU 正在访存, 则需等待 CPU 存取结束后, 再让出总线控制权

- 如果两者同时申请, 则 DMA 优先获取控制权(避免数据缓冲寄存器满后数据丢失)

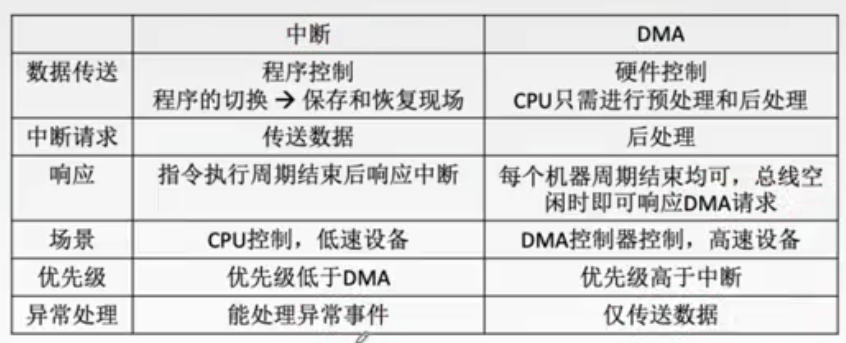

DMA 与中断的比较 #

- IO 系统基本概念

- I/O 控制方式

- 外部设备

- 输入设备

- 输出设备

- 外部存储器

- IO 接口

- 基本结构

- 编址

- 统一编址

- 独立编址

- IO方式(可能出综合题)

- 程序查询方式

- 工作流程

- 计算例题

2.程序中断方式(可能考大题) - 中断的分类

- 中断的硬件向量

- 中断的处理过程

- 单中断与多中断

- 中断屏蔽技术

- DMA 方式

- DMA 的结构

- DMA 的工作过程

- DMA 的特点

- DMA 与中断的比较

- 程序查询方式